#### Praktikum

# "Schaltungsdesign mit FPGA"

Karlsruhe, den SS 2013

Postanschrift: Institut für Mikro- und Nanoelektronische Systeme Tel.: +49 (0) 721 608 4 49 61 +49 (0) 721 608 4 49 61

Fax.: +49 (0) 721 75 79 25 Email: doris.duffner@kit.edu

WWW: http://www.ims.kit.edu

Hertzstraße 16

D - 76128 Karlsruhe

Gebäude: Hertzstraße 16, Geb. 06.41

## Inhaltsverzeichnis

| 1 | Einl | eitung                                                  | 1  |

|---|------|---------------------------------------------------------|----|

|   | 1.1  | Versuchsdurchführung und Benotung                       | 1  |

| 2 | Gru  | ndlagen                                                 | 3  |

|   | 2.1  | PAL's                                                   | 3  |

|   | 2.2  | GAL's                                                   | 7  |

|   | 2.3  | EPLD's                                                  | 7  |

|   | 2.4  | FPGA's                                                  | 10 |

|   |      | 2.4.1 Die Bausteinserie Cyclone II                      | 14 |

|   |      | 2.4.1.1 Prinzipieller Aufbau der Cyclone II Serie       | 16 |

|   |      | 2.4.1.1.1 Logic Array Block (LAB)                       | 16 |

|   |      | 2.4.1.1.2 Logikelement (LE)                             | 16 |

|   |      | 2.4.1.1.3 Embedded Array Block                          | 22 |

| 3 | Eing | gabe von Schaltungsinformationen                        | 24 |

|   | 3.1  | VHDL als Standardsprache                                | 24 |

|   | 3.2  | AHDL (Altera Hardware Description Language)             | 30 |

| 4 | Kur  | zeinführung in Altera Quartus II                        | 31 |

|   | 4.1  | Projektverwaltung                                       | 31 |

|   | 4.2  | Grafische Eingabe (Block Diagram/Schematic)             | 33 |

|   |      | 4.2.1 Erstellen von Symbolen (Block Symbol)             | 33 |

|   | 4.3  | Erstellen von Textdateien (AHDL File oder VHDL File)    | 33 |

|   | 4.4  | Erstellen von Simulationsstimuli (Vector Waveform File) | 34 |

|   |      | 4.4.1 Einrichtung der VWF Editor ab Quartus II v11.1    | 34 |

|   | 4.5  | Zuweisungen (Assignments)                               | 34 |

|   | 4.6  | Compiler und Simulator                                  | 34 |

|   |      | 4.6.1 Ergebnisfenster (Reports)                         | 35 |

|   | 4.7  | Programmierung                                          | 35 |

| 5 | Die  | Entwicklungsumgebung im Praktikum                       | 36 |

|   |      | Das Altera DSP Entwicklungs–Board                       | 36 |

|   |      | 5.1.1 Der Altera EP2C70F672 Baustein                    | 38 |

|   |      | 5.1.1.1 Das Logic Element (LE)                          | 38 |

|   |      | 5.1.1.2 Der Logic Array Block (LAB)                     | 38 |

|   |      | 5.1.1.3 Die MegaLAB-Struktur                            | 39 |

|   |      | 5.1.1.4 Der Embedded System Block (ESB)                 | 39 |

|   |      | 5 1 1 5 Globale Signale                                 | 40 |

|   |      | 5.1.2   | Taktung und PLLs                        |    |

|---|------|---------|-----------------------------------------|----|

|   |      | 5.1.3   | A/D-Wandler                             | 12 |

|   |      | 5.1.4   | D/A-Wandler                             | 12 |

|   |      | 5.1.5   | Speicherbausteine                       | 15 |

|   |      | 5.1.6   | Schalter und Taster                     | 17 |

|   |      | 5.1.7   | Leuchtdioden                            | 19 |

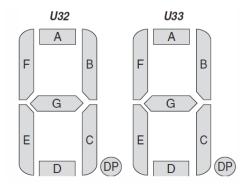

|   |      | 5.1.8   | Sieben-Segment-Anzeige                  | 50 |

| 6 | Proj | jekt Fa | ltungscodierer 5                        | 2  |

|   | 6.1  | Theor   | ie                                      | 52 |

|   |      | 6.1.1   | Codierung                               | 52 |

|   |      |         | 6.1.1.1 Faltungscodierung               | 55 |

|   |      |         | 6.1.1.2 Registerdarstellung             | 55 |

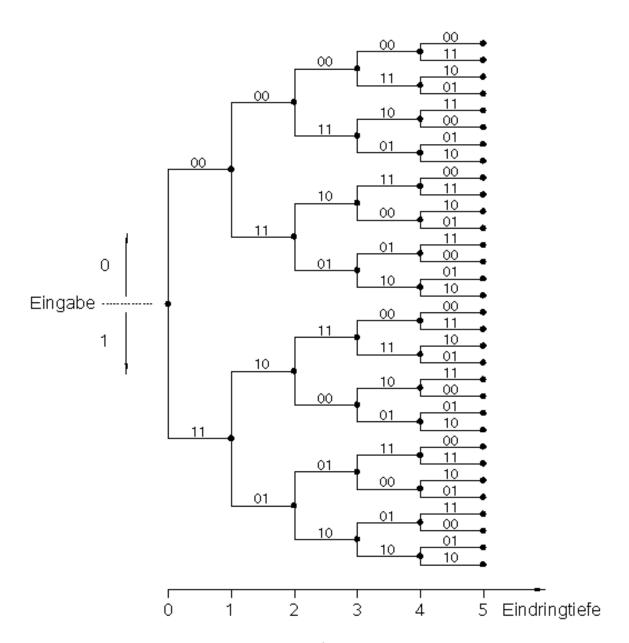

|   |      |         | 6.1.1.3 Codebaum                        | 56 |

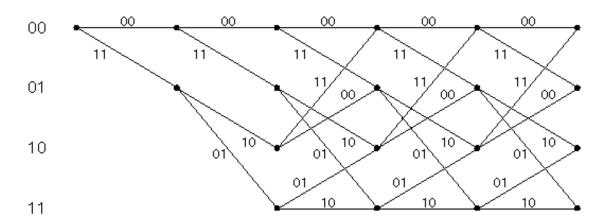

|   |      |         | 6.1.1.4 Netzdiagramm                    | 56 |

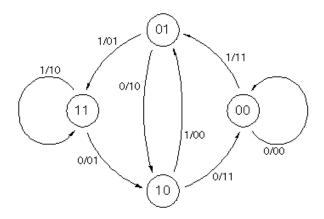

|   |      |         | 6.1.1.5 Zustandsdiagramm                | 56 |

|   |      |         | 6.1.1.6 Mathematische Darstellung       | 58 |

|   | 6.2  | Versuc  | ch Faltungscodierer                     | 31 |

|   |      | 6.2.1   | Encoder mit Schieberegister erstellen 6 | 32 |

|   |      | 6.2.2   | Encoder mit VHDL erstellen              | 32 |

|   |      | 6.2.3   | Encoder mit AHDL erstellen              | 3  |

|   |      | 6.2.4   | Vergleich der Entwürfe                  | 3  |

| 7 | Proj | jekt La | uflicht 6                               | 4  |

| 8 | Proi | iekt Di | gitale Filter 6                         | 5  |

|   | 8.1  |         | _                                       |    |

|   |      | 8.1.1   | Projektverwaltung                       |    |

|   |      |         | •                                       | 35 |

|   |      |         | g .                                     | 35 |

|   |      | 8.1.2   |                                         | 35 |

|   |      |         |                                         | 66 |

|   |      |         |                                         | 66 |

|   |      |         |                                         | 66 |

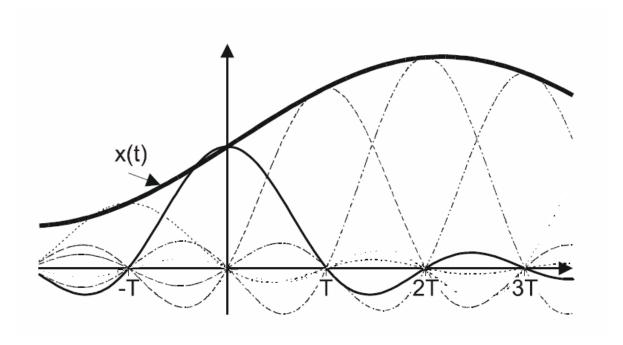

|   |      |         | 8.1.2.1.3 Signalrekonstruktion 6        | 57 |

|   |      |         |                                         | 37 |

|   |      |         | 8.1.2.2 Diskrete Signale                | 37 |

|   |      |         |                                         | 38 |

|   |      |         | 9                                       | 39 |

|   |      |         |                                         | 39 |

|   |      |         |                                         | 70 |

|   |      |         | 8.1.2.3 Diskrete Systeme                |    |

|   |      |         |                                         | 70 |

|   |      |         | 8.1.2.3.1 Beschreibung im Zeitbereich   |    |

|     |       | 8.1.2.3.4 Pole und Nullstellen als Systembesch      | reibung |   |   | 72  |

|-----|-------|-----------------------------------------------------|---------|---|---|-----|

|     |       | 8.1.2.4 Zahlendarstellung                           |         |   |   | 72  |

|     |       | 8.1.2.4.1 Natürliche Zahlen                         |         |   |   | 73  |

|     |       | 8.1.2.4.2 Positive Festkommazahlen                  |         |   |   | 73  |

|     |       | 8.1.2.4.3 Zweierkomplementdarstellung               |         |   |   | 73  |

|     |       | 8.1.2.4.4 Festkommadarstellung                      |         |   |   | 74  |

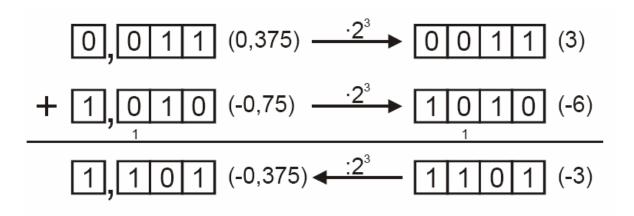

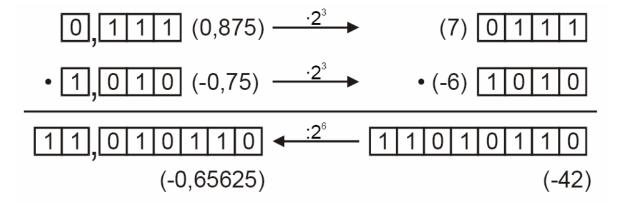

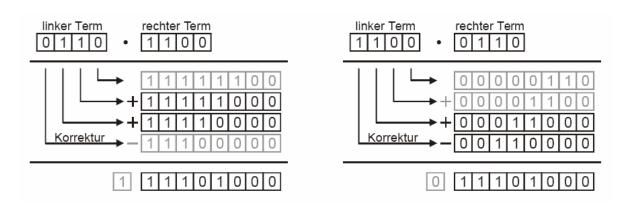

|     |       | 8.1.2.5 Rechenoperationen in Festkommadarstellung . |         |   |   | 75  |

|     |       | 8.1.2.5.1 Bitbreitenänderung                        |         |   |   | 75  |

|     |       | 8.1.2.5.2 Addition/Subtraktion                      |         |   |   | 76  |

|     |       | 8.1.2.5.3 Multiplikation                            |         |   |   | 78  |

|     |       | 8.1.2.6 Gleitkommazahlen                            |         |   |   | 80  |

|     |       | 8.1.2.7 Blockgleitkommazahlen                       |         |   |   | 80  |

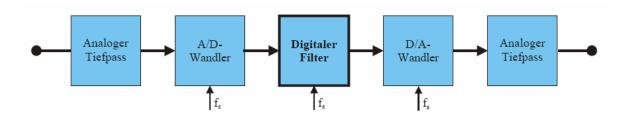

|     | 8.1.3 | Digitale Filter                                     |         |   |   | 80  |

|     | 0.1.0 | 8.1.3.1 Grundlagen digitale Filter                  |         |   |   | 81  |

|     |       | 8.1.3.1.1 Umgebung von digitalen Filtern            |         |   |   | 81  |

|     |       | 8.1.3.2 Elemente der Digitalfilter                  |         |   |   | 82  |

|     |       | 8.1.3.2.1 Systemfunktion                            |         |   |   | 82  |

|     |       | 8.1.3.2.2 Frequenzgang                              |         |   |   | 83  |

|     |       | 8.1.3.2.3 Anordnung der Elemente                    |         |   |   | 83  |

|     |       | 8.1.3.2.4 Filterordnung                             |         |   |   | 85  |

|     |       | 8.1.3.3 Stichwort Echtzeitsystem                    |         |   |   | 85  |

|     |       | 8.1.3.4 Pipelining                                  |         |   |   | 85  |

|     |       | 8.1.3.5 FIR-Filter                                  |         |   |   | 85  |

|     |       | 8.1.3.5.1 Eigenschaften der FIR–Filter              |         |   |   | 87  |

|     |       | 8.1.3.6 IIR-Filter                                  |         |   |   | 88  |

|     |       | 8.1.3.6.1 Vergleich mit IIR-Filternn                |         |   |   | 88  |

|     |       | 8.1.3.6.2 Parallele Realisierung                    |         |   |   | 89  |

|     |       | 8.1.3.6.3 Serielle Realisierung                     |         |   |   | 90  |

|     |       | 8.1.3.6.4 Gemischte Realisierung                    |         |   |   | 90  |

|     |       | 8.1.3.7 Beispiele einfacher FIR-Filter              |         |   |   | 91  |

|     |       | 8.1.3.7.1 FIR—Filter erster Ordnung                 |         |   |   | 92  |

|     |       | 8.1.3.7.2 Tiefpass erster Ordnung                   |         |   |   | 92  |

|     |       | 8.1.3.8 Hochpass erster Ordnung                     |         |   |   | 92  |

|     |       | 8.1.3.9 FIR-Filter zweiter Ordnung                  |         |   |   | 93  |

|     |       |                                                     |         |   |   | 93  |

|     |       | 1                                                   |         |   |   |     |

|     |       | 8.1.3.10 Hochpass zweiter Ordnung                   |         |   |   | 94  |

|     |       | 8.1.3.11 Bandpass und Bandsperre zweiter Ordnung .  |         |   |   | 95  |

|     |       | 8.1.3.12 Design von FIR-Filtern höherer Ordnung     |         |   |   | 98  |

|     |       | 8.1.3.12.1 Spezifikation der Filtereigenschaften    |         |   |   | 98  |

| 0.0 | 17    | 8.1.3.12.2 Approximation des Frequenzganges .       |         |   |   | 99  |

| 8.2 |       | che mit FIR-Filtern zweiter Ordnung                 |         |   |   |     |

|     | 8.2.1 | Tiefpass erstellen                                  |         |   |   |     |

|     | 8.2.2 | Hochpass erstellen                                  |         |   |   |     |

|     | 8.2.3 | Bandpass                                            |         | • | • | 104 |

|     |       |                                                     |         |   |   |     |

| 8.2.4 | Bandsperre                              |

|-------|-----------------------------------------|

| 8.2.5 | Projekt mit allen Filtern               |

| 8.2.6 | Programmierung des Cyclone II Bausteins |

### 1 Einleitung

In der digitalen Schaltungstechnik werden heute neben den bekannten Serien von Logikbausteinen niedriger bis mittlerer Komplexität bzw. Integrationsdichte in bipolaren und Feldeffekt- Technologien wie TTL-Logik-Familien, ECL-Familien und CMOS-Reihen immer mehr programmierbare Logikbausteine eingesetzt.

Diese programmierbaren Bausteine liegen in der Komplexität zwischen diesen Standard-Logik-Serien und den kundenspezifischen integrierten Logikschaltungen, wie sie z.B. in Mikrorechnersystemen eingesetzt werden.

Während das Arbeiten mit den Standard-Serien auf einem Logikentwurf mit bestimmten bekannten und festgelegten Funktionen basiert, hat man beim Einsatz von programmierbaren Logikbausteinen die Möglichkeit, die verschiedensten logischen Funktionen auf einem einzigen Baustein zu realisieren. Je nach Art und Aufbau des Logikbausteins kann man damit bis zu 100 Standardbausteine ersetzen.

Dies beinhaltet jedoch ein fundiertes Wissen über den logischen Aufbau dieser Bausteine und umfangreiche Hilfsmittel von der Eingabe der Schaltung über die Simulation bis zur Programmierung der Bausteine.

In diesem Praktikum soll der Umgang mit verschiedenen Typen von programmierbaren Logikbausteinen anhand von Beispielen erlernt und geübt werden. Hierzu wurde ein Entwicklungssystem der Firma ALTERA gewählt, da hier eine große Auswahlmöglichkeit unter verschiedenen Bausteinfamilien gegeben ist.

### 1.1 Versuchsdurchführung und Benotung

Das Praktikum wird im CIP-Pool der Westhochschule, Geb. 06.41 Raum 102, durchgeführt. Sie benötigen dafür Ihren Stud-Account und einen USB Stick für die lokale Datenspeicherung, da die Sicherheitsrichtlinien des RZ es leider unmöglich machen, Ihnen Speicherplatz auf dem Institutsserver zu überlassen. Die verfügbare Speichergröße des USB Sticks sollte mindestens 256 MB betragen. Das Praktikum beinhaltet drei unterschiedliche Projekte (Faltungscodierer, LED-Lauflicht und digitale Filter) mit entsprechenden Unterprojekten. Die Beschreibungen zu jedem Versuch mit einem Theorieteil finden Sie ab Kapitel 6 dieses Skriptes. Daraus werden sechs Teilnoten gebildet. Die siebte Teilnote ergibt sich aus dem Praktikumsbericht, der nach Ende des Praktikums zu erstellen ist. Halten Sie Ihre Praktikumsergebnisse deshalb in einem schriftlichen Bericht mit Screenshots und Ausarbeitung Ihrer Ergebnisse bzw. Schlussfolgerung fest und geben sie diesen nach Ende des Praktikums per Email beim Betreuer ab. Die Gesamtnote

ergibt sich dann aus dem geometrischen Mittel der Teilnoten.

### 2 Grundlagen

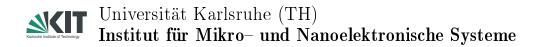

In diesem Kapitel sollen die Bezeichnungen bzw. Gruppen der Logikbausteine erläutert und auf den prinzipiellen schaltungstechnischen Aufbau eingegangen werden. Die programmierbaren Logikbausteine lassen sich nach Bild 2.1 grob wie folgt einteilen: Die Grundlage für die Entwicklung programmierbarer Logikbausteine ist das PROM,

Bild 2.1: Grobe Übersicht der programmierbaren Logikbausteine.

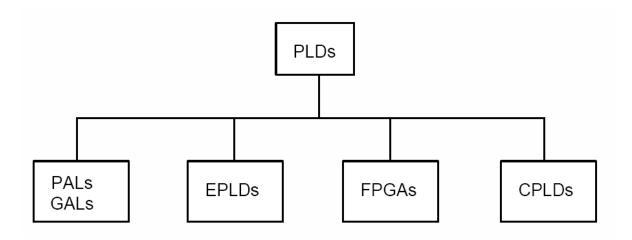

ein vom Anwender einmalig programmierbarer Speicherbaustein. Ein Vergleich der Programmierschemata (Bild 2.2) soll die wesentlichen Unterschiede der Bausteinfamilien aufzeigen. Bei einem PROM stellen die Eingänge Adressen dar, deren Inhalt bei entsprechender Auswahl am Ausgang abgegriffen werden kann. Bei einem PAL-Baustein sind die Ausgangssignale fest zugeordnet, während die Aufteilung der Eingänge vom Anwender festgelegt werden kann. Den höchsten Freiheitsgrad für den Anwender bieten die FPGAs, denn hier kann sowohl das UND-Array auf der Eingangsseite wie auch das ODER-Array auf der Ausgangsseite programmiert werden.

Zur Gruppe der CPLDs (Complex Programmable Logic Device) gehören die LCAs (Logic Cell Arrays) der Firmen Xilinx und AMD und die EPLDs (Erasable Programmable Logic Device) und die FLEX-Bausteinserie von ALTERA. Diese werden in einem späteren Kapitel ausführlich beschrieben.

#### 2.1 PAL's

Die erste Gruppe von programmierbaren Logikbausteinen auf dem Markt wurden mit der Bezeichnung PAL (**P**rogrammable **A**rray **L**ogic) versehen.

Bild 2.2: Schematische Struktur eines PROMs, PALs und FPGAs (v. l. n. r.).

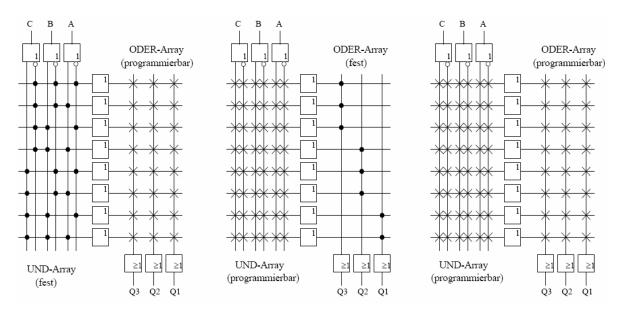

Bild 2.3: Blockschaltbild und logisches Symbol eines PAL 16R8.

| PAL | $\mathbf{X}$ | nn | $\mathbf{y}$ | $\mathbf{m}\mathbf{m}$ | -tt | $\mathbf{T}$ | $\mathbf{P}$ |

|-----|--------------|----|--------------|------------------------|-----|--------------|--------------|

|-----|--------------|----|--------------|------------------------|-----|--------------|--------------|

| x: Eingangsregister-Typ                        | ohne Bez.: kein Eingangsregister |

|------------------------------------------------|----------------------------------|

|                                                | R: D-Flipflop                    |

|                                                | T: transparentes Flipflop        |

| nn: Anzahl der Eingänge des Eingangsfeldes     |                                  |

| y: Angaben zum Ausgang                         | R: mit Ausgaberegister           |

|                                                | L: Ausgang aktiv LOW             |

|                                                | X: Ausgang EXOR-verknüpft        |

|                                                | V: Variabler Ausgang,            |

|                                                | z.B. über Makrozelle             |

| mm: Anzahl der Ausgänge des Bausteins          |                                  |

| -tt: Angabe über Geschwindigkeit des Bausteins | Laufzeit (in ns) oder Ziffer     |

| T: Angabe über Temperaturbereich               | z.B.: C: 0 70°C                  |

|                                                | M: -55 +125°C                    |

| P: Angabe über Gehäusetyp und -material        | N: DIP, Plastik                  |

|                                                | J: DIP, Keramik                  |

|                                                | NW: DIP 600-mil, Plastik         |

|                                                | FN: Chip Carrier, Plastik        |

|                                                | FK: Chip Carrier, Keramik        |

|                                                | u.a.m.                           |

Tabelle 2.1: Aufgeschlüsselter Zahlen- und Buchstabencode von PALs.

Ein PAL ist ein durch den Benutzer programmierbarer Baustein auf der Basis von schmelzbaren Mikro-Brücken (wie bei den PROMs). Die Eingänge können über programmierbare UND-Funktionen miteinander verknüpft werden deren Ausgänge über festverdrahtete ODER-Funktionen verknüpft sind. Die Bausteine sind mit einem Zahlenund Buchstabencode bezeichnet, welchem genaue Aussagen über den internen Aufbau zu entnehmen sind (vgl. Tabelle 2.1). Ein Baustein mit der Bezeichnung PAL 16 R 8 -12 C N hat also ein Eingangsfeld mit 16 Eingängen ohne Register, 8 Ausgänge mit Register, 12 ns Gatterlaufzeit, ist für einen Temperaturbereich von 0 bis 70° C spezifiziert und ist in einem Standard Dual-In-Line Plastikgehäuse mit 0,3" Abstand der Pinreihen.

Neben der Bezeichnung PAL existieren für bestimmte Funktionen weitere Bezeichnungen, wie z.B. PAD = Programmierbarer Adreßdekoder, PSL = Programmierbare Sequenz Logik. Diese Bezeichnungen können jedoch von Herstellerfirma zu Herstellerfirma unterschiedlich sein.

Nach dieser Erklärung soll der prinzipielle Aufbau eines PAL anhand von logischen Symbolen und Schaltbildern näher betrachtet werden. Bild 2.3 zeigt das Logische Symbol eines PAL 16R8 Bausteins. Die oben beschriebenen 16 Eingänge des UND/ODER–Arrays setzen sich aus 8 Eingängen des Bausteins (In1–In8) und aus den Rückführungen der 8 Flipflops am Ausgang des UND/ODER–Arrays zusammen. In dem UND/ODER–

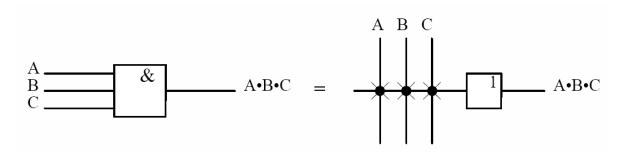

Bild 2.4: Beispiel einer UND-Verknüpfung.

Bild 2.5: Logisches Schaltbild und Realisierung der Verknüpfung zweier Eingänge bei einem.

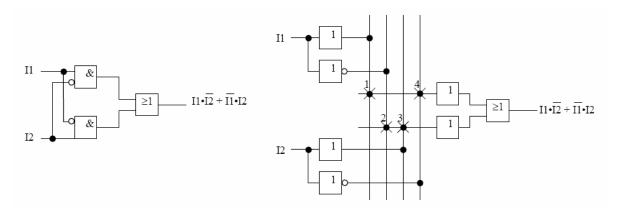

Array werden logische Verknüpfungen durch die Programmierung eines Knotens realisiert. Bei einem PAL-Baustein ist dieser Knoten zunächst ein intakter Knoten, d.h. es besteht eine elektrische Verbindung am Kreuzungspunkt der Leitungen, die beim Programmieren zerstört wird wenn keine elektrische Verbindung hergestellt werden soll. Anhand der Beispiele in Bild 2.4 und Bild 2.5 sollen einfache logische Verknüpfungen und deren Realisierung mit einem programmierbaren Logikbaustein gezeigt werden. Die durchkreuzten Punkte stellen dabei programmierbare Knoten dar. Von den in Bild 2.5 dargestellten 4 programmierbaren Knoten (1-4) bleiben je nach gewünschter Funktion 2 bestehen, während die anderen beiden zerstört werden müssen. Soll z.B. eine ODER-Verknüpfung realisiert werden, so dürfen nach dem Programmieren nur noch die Verbindungen der Knoten 1 und 3 bestehen bleiben.

Der prinzipielle Aufbau eines PAL-Bausteins mit Ausgangsregistern ist in Bild 2.6 dargestellt. Das Ergebnis der sogenannten Produktterme wird mit der ansteigenden Flanke des Taktsignals im Ausgangs-D-Flipflop gespeichert. Wenn der Ausgangstreiber freigegeben ist, wird die Information am Q-Ausgang des Registers invertiert am Ausgangspin des Bausteins anliegen. Gleichzeitig wird die Ausgangsinformation sowohl invertiert wie auch nichtinvertiert zurückgeführt und kann bei entsprechender Programmierung des Bausteins beim nächsten Taktschritt als Eingangsinformation verwendet

Bild 2.6: Darstellung der Struktur eines Eingangs und Ausgangs des PAL 16R8.

werden. Damit können unter anderem auch Funktionen wie Zählen und Schieben realisiert werden. Das Ausgangsregister in Bild 2.6 kann bei anderen Ausführungen von PLDs auch fehlen, bzw. durch eine sogenannte Makrozelle, welche im allgemeinen sowohl ein Eingangs- wie auch ein Ausgangsregister besitzt und an einen I/O-Pin des Bausteins führt.

#### 2.2 GAL's

Eine Erweiterung der Gruppe der PALs hat die Bezeichnung GAL (Generic Array Logic). Sie besitzen im wesentlichen die gleiche Struktur, haben jedoch gegenüber den PAL-Bausteinen ein- und ausgangsseitig eine erheblich erweiterte Matrix.

#### 2.3 EPLD's

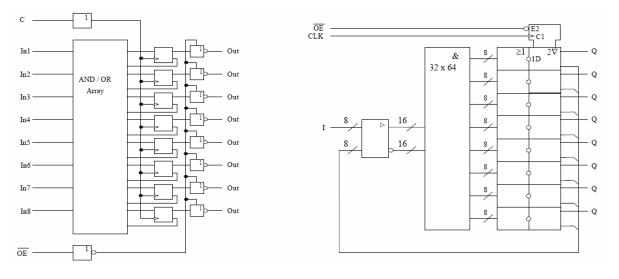

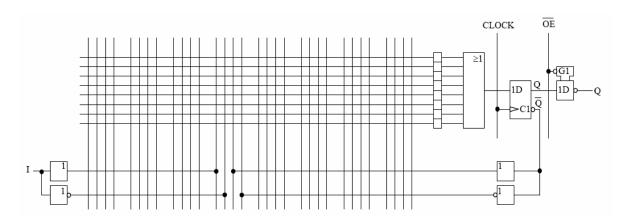

Die nächst komplexere Bausteinfamilien sind die EPLDs. Sie basieren im allgemeinen auf einer CMOS EPROM-Technologie, d.h. diese Bausteine können im Gegensatz zu den PALs mehrfach programmiert werden, da sie wie ein normales EPROM mit ultraviolettem Licht gelöscht werden können. In neueren Bausteinserien wird inzwischen die EEPROM-Technik eingesetzt, d.h. das Löschen erfolgt hierbei elektrisch. Damit entfällt die aufwendige Gehäusetechnik der EPROMs, die ja ein Quartzglasfenster besitzen müssen. Die EPLDs sind aus sogenannten Makrozellen aufgebaut, die durch eine Art Bus miteinander verbunden sind. Die Komlexität reicht von 8 bis hin zu mehreren Hundert Makrozellen, also von einem bis zu einigen Zehn PALs. Damit lassen sich schon recht umfangreiche Logikfunktionen auf einem einzigen Baustein realisieren. Die prinzipiellen Strukturen dieser Bausteine sollen anhand einiger Darstellungen näher erläutert werden.

Die EPLD-Bausteine besitzen im allgemeinen einige reine Eingänge und eine Reihe von Ein- und Ausgängen. Die speziellen Takteingänge führen direkt zu den Makrozellen.

Bild 2.7: Aufbau eines sogenannten klassischen EPLDs.

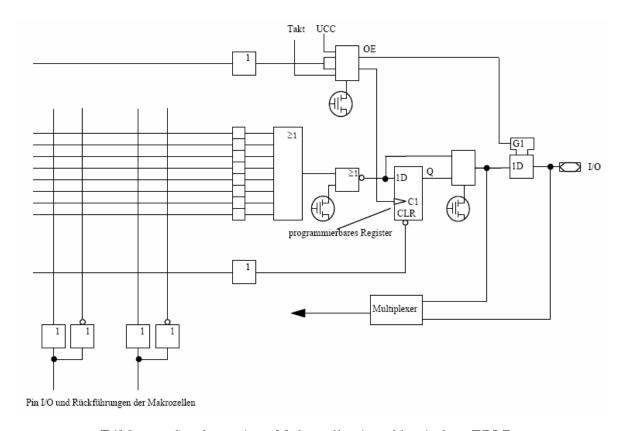

Selbstverständlich kann auch an jeden anderen Eingang ein Taktsignal angelegt werden. Die Makrozellen besitzen alle ein frei programmierbares Flipflop, das vom Anwender entweder als D-, T-, SR- oder JK-Flipflop oder als Element für kombinatorische Logik eingesetzt werden kann. Die programmierbare UND/feste ODER-Logik kann zur Implementierung von Logikelementen mit bis zu 8 Produkttermen eingesetzt werden. Die programmierbare Ein-Ausgangs-Logik kann sowohl für Signale mit aktivem HIGH-Pegel wie auch mit aktivem LOW-Pegel verwendet werden. Den Aufbau einer Makrozelle zeigt Bild 2.8.

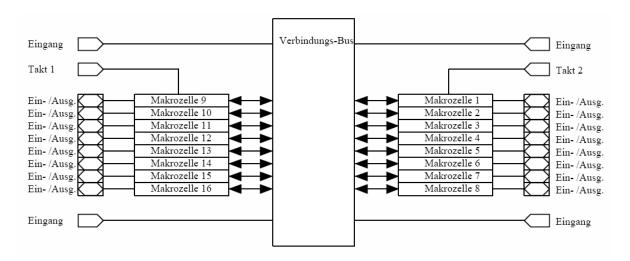

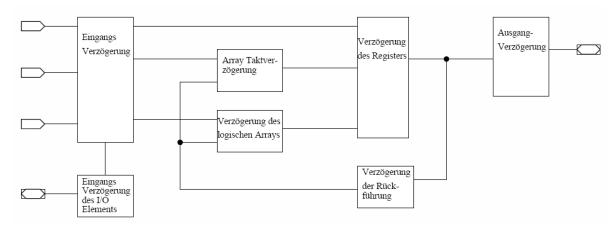

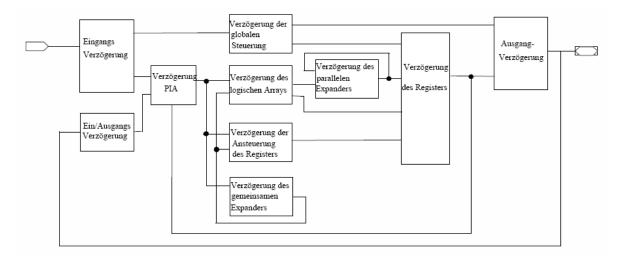

Durch die höhere Komlexität der EPLDs ist es notwendig, vor der endgültigen Auswahl des verwendeten Bausteins, sich einen Überblick zu verschaffen, welche zeitlichen Verzögerungen innerhalb des Bausteins zwischen Eingang und Ausgang auftreten können. Dazu soll das Übersichtsschema in Bild 2.9 herangezogen werden. Der Übergang von den klassischen programmierbaren Bausteinen zu den komplexen PLDs ist fließend. Die Frage, ab welcher Anzahl vom Makrozellen oder ab welcher Zahl von Produkttermen ein Baustein als komplexer Baustein zu bezeichnen ist kann in dieser Form nicht beantwortet werden. Die Struktur dieser EPLDs soll am Beispiel eines EPLDs aus der Serie MAX7000 erläutert werden (Bild 2.10).

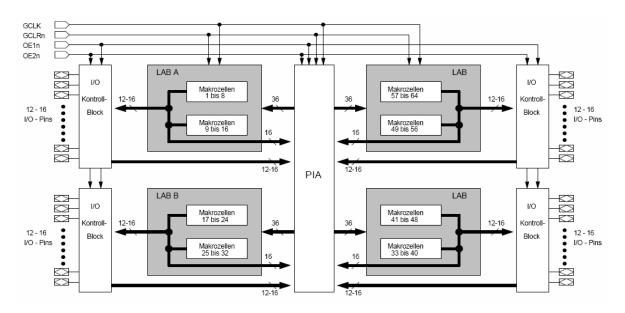

Der Baustein MAX7064 besitzt 64 Makrozellen und hat eine programmierbare I/O-Architektur mit bis zu 68 Eingängen oder 64 Ausgängen. Die Auffächerung der Produktterme der Expander ist konfigurierbar und erlaubt bis zu 32 Produktterme in einer einzelnen Makrozelle. Der Baustein besitzt 1250 Gatteräquivalente und kann mit bis zu 125 MHz getaktet werden. Die Makrozellen dieser Bausteine werden zu sogenannten "Logical Array Blocks" (LABs) zusammengefaßt. Die Makrozellen selbst besitzen ein programmierbares UND/festes ODER-Array und ein frei konfigurierbares Register, das Möglichkeiten wie einen unabhängigen, programmierbaren Takteingang, einen Taktfreigabeeingang und Lösch- und Setzfunktionen bietet. Die LABs und damit die

Bild 2.8: Struktur einer Makrozelle eines klassischen EPLDs.

**Bild 2.9:** Schema der Signallaufzeiten zwischen Eingang und Ausgang eines klassischen EPLDs.

Bild 2.10: Aufbau eines MAX7064 EPLD-Bausteins.

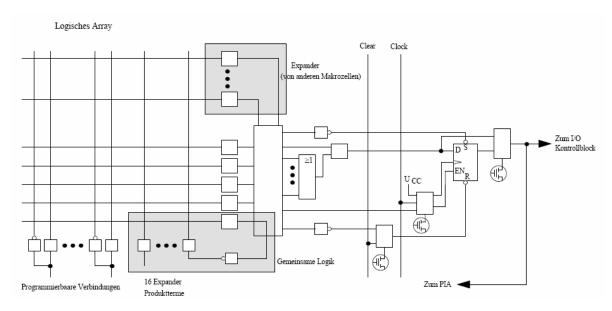

Makrozellen können über ein "Programmable Interconnect Array" (PIA) untereinander verbunden werden. Den schematischen Aufbau der beschriebenen Makrozelle zeigt Bild 2.11. Auch für diese EPLDs soll ein Übersichtsschema der zeitlichen Verzögerung der Signale zwischen Ein- und Ausgang angegeben werden. Gegenüber den klassischen EPLDs ist der Signallaufplan deutlich komplexer.

#### 2.4 FPGA's

Die nächste Serie der programmierbaren Bausteine sind die FPGAs (Field Programmable Gate Arrays). Als programmierbare Elemente werden hierbei statische RAM-Zellen eingesetzt. Zu dieser Gruppe von Bausteinen zählen alle LCAs (Logic Cell Arrays) und die FLEX-Serie (Flexible Logic Element Matrix) der Firma Altera. Die Komplexität dieser Bauelemente reicht von einigen Hundert bis zu einigen Zehntausend Gatteräquivalenten. Diese Bausteine haben jedoch gegenüber den bisher beschriebenen einen Nachteil: sie verlieren beim Abschalten der Versorgungsspannung ihre Information und müssen deshalb nach jedem Einschalten neu programmiert werden. Dies kann direkt über eine Programmierschnittstelle erfolgen, oder durch ein sogenanntes Konfigurations-EPROM, in dem die Information fest gespeichert ist.

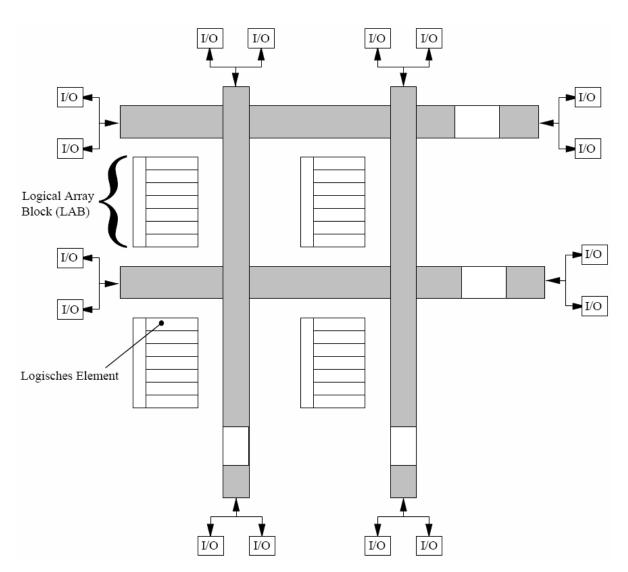

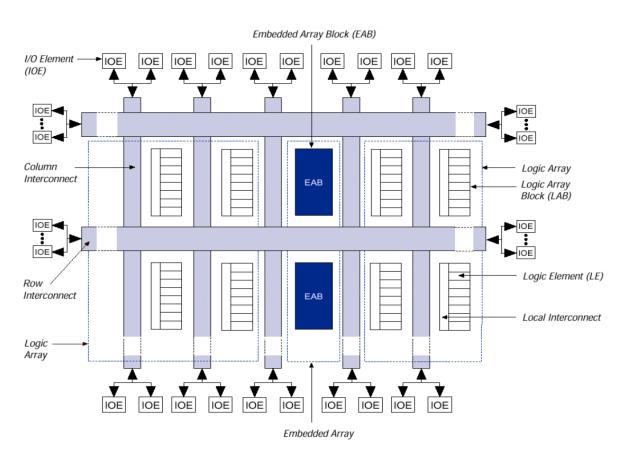

Der prinzipielle Aufbau dieser Bausteine soll anhand der FLEX 8000-Serie näher beschrieben werden. Zwischen den Ein-Ausgabe-Elementen an den Rändern des ICs verlaufen horizontal und vertikal durchgehende Bereiche mit Leitungen, über welche alle Verbindungen von und nach außen laufen. Zwischen den Bereichen mit den Leiterbahnen liegen sogenannte LABs (Logical Array Blocks), welche sich wiederum aus einzelnen logischen Elementen zusammensetzen. Ein Logic Array Block (LAB) besteht

Bild 2.11: Struktur einer Makrozelle.

**Bild 2.12:** Schema der Signallaufzeiten zwischen Eingang und Ausgang eines EPLDs der Serie MAX7000.

Bild 2.13: Blockschaltbild des Aufbaus der FLEX 8000 Serie.

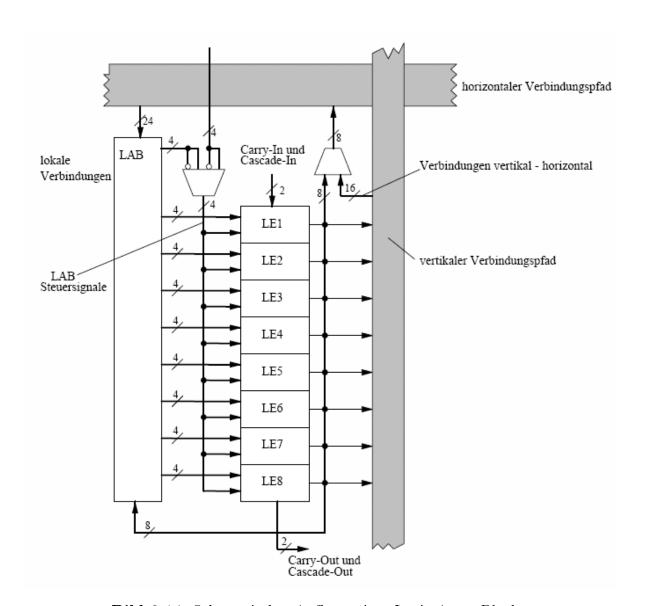

aus acht logischen Elementen, den zugehörigen Carry und Cascade Pfaden, den LAB-Steuersignalen und einem lokalen Verbindungsblock. Diese Grundstruktur des Bauelements ist in Bild 2.13 schematisch dargestellt. Die Eingangsdaten für die Elemente werden entweder aus den horizontalen Verbindungsbereichen oder von speziellen Eingangspins direkt geliefert. Die Ausgänge der Logischen Elemente werden sowohl zu den horizontalen wie auch den vertikalen Verbindungsbereichen und zu den Eingangsverknüpfungen des LAB geführt.

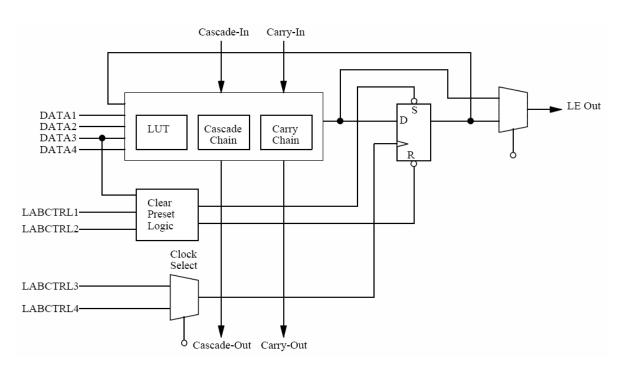

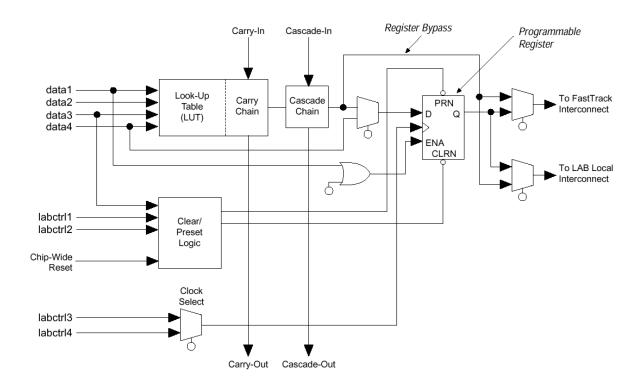

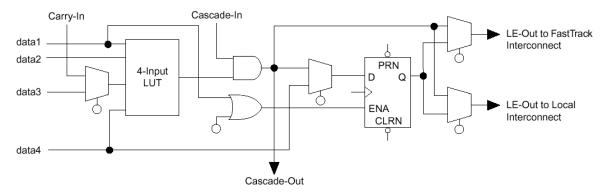

Das Logikelement ist die kleinste logische Einheit eines FLEX 8000-Bausteins. Jedes dieser Elemente enthält eine "look-up table (LUT)" mit 4 Eingängen, je ein Element für Übertrags- und Kaskadiersignale (Carry Chain, Cascade Chain) und ein programmierbares Flipflop, das als D-, T-, JK- oder SR-FF eingesetzt werden kann. Die LUT ist eine Art von Funktionsgenerator, der aus den 4 Eingangsvariablen jede logische Verknüpfung

Bild 2.14: Schematischer Aufbaus eines Logic Array Blocks.

Bild 2.15: Blockschaltbild eines Logikelements.

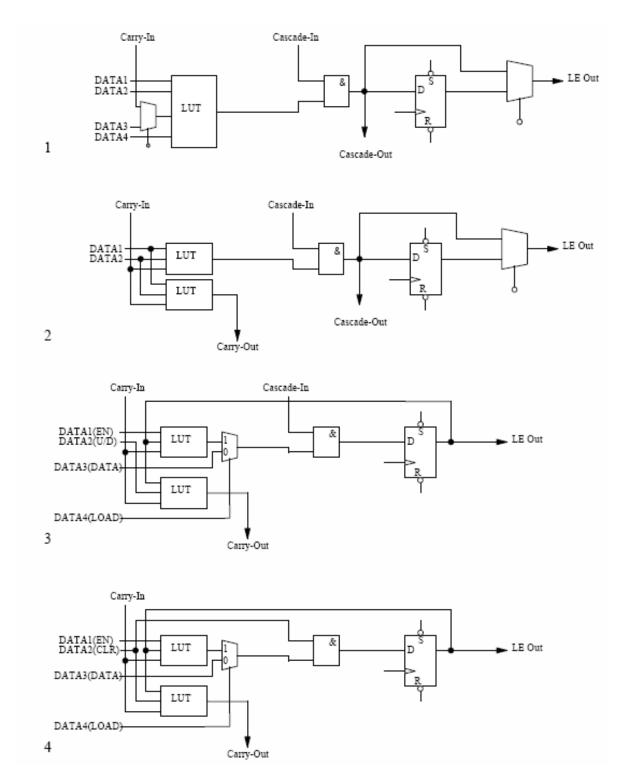

erzeugen kann. Wird ein Logikelement ausschließlich für kombinatorische Logik eingesetzt, so wird der Ausgang der LUT am Flipflop vorbei, direkt zum Ausgang geführt. Die beiden Datenpfade Carry und Cascsade sind Hochgeschwindigkeitsverbindungen zwischen den einzelnen Logikelementen. Der Carry Pfad unterstützt die Entwicklung von Zählern mit hohen Taktfrequenzen und der Cascade Pfad implementiert breitgefächerte Eingangsfunktionen mit einem Minimum an Laufzeitverlusten. Ein Logikelement kann in vier verschiedenen Betriebsarten eingesetzt werden:

- 1. "Normaler Betrieb",

- 2. "Arithmetische Betriebsart",

- 3. "Vorwärts/Rückwärts Zähler" und

- 4. "Rücksetzbarer Zähler".

Die zugehörigen Signalpfade sind in Bild 2.16 dargestellt. Betriebsart 1 ist geeignet für allgemeine logische Anwendungen und für Dekodierschaltungen mit vielen Eingängen, die den Vorteil des Kaskadiersignals ausnutzen können. Hierbei werden die vier Dateneingänge und das Carry–In Signal als Eingangssignale für das Logische Element benutzt. Für das Carry–In Signal wird vom MAX+PLUSII Compiler immer der Eingang DATA3 ausgewählt.

#### 2.4.1 Die Bausteinserie Cyclone II

Der Cyclone II Baustein gehört zur Familie der FPGAs (Field Programmable Gate

Bild 2.16: Signalverläufe bei den verschiedenen Betriebsarten eines Logischen Elements.

| Kennzeichen            | EP2C5  | EP2C8  | EP2C15 | EP2C20 | EP2C35 | EP2C50 | EP2C70  |

|------------------------|--------|--------|--------|--------|--------|--------|---------|

| Logikelemente (LEs)    | 4608   | 8256   | 14448  | 18752  | 33216  | 50528  | 68416   |

| M4K RAM blocks         | 26     | 36     | 52     | 52     | 105    | 129    | 250     |

| Total RAM bits         | 119808 | 165888 | 239616 | 239616 | 483840 | 594432 | 1152000 |

| Embedded multipliers   | 13     | 18     | 26     | 26     | 35     | 86     | 150     |

| PLLs                   | 2      | 2      | 4      | 4      | 4      | 4      | 4       |

| Max. Benutzer I/O Pins | 158    | 182    | 315    | 315    | 475    | 450    | 622     |

Tabelle 2.2: Bausteinübersicht der Serie Cyclone II.

Arrays). Als programmierbare Elemente werden hierbei statische RAM-Zellen eingesetzt. Zu dieser Gruppe von Bausteinen zählen alle LCAs (Logic Cell Arrays), eben auch die Cyclone II von Altera. Die Komplexität dieser Bausteine reicht von einigen Tausend bis zu einigen Zehntausend Gatteräquivalenten. Eine kleine Baustainübersicht ist in Tabelle 2.2 dargestellt. Diese Bausteine haben jedoch gegenüber den PLDs (Programmable Logic Devices) einen Nachteil. Sie verlieren beim Abschalten der Versorgungsspannung Ihre Informationen und müssen deshalb nach jedem erneuten Einschalten der Versorgungsspannung neu programmiert werden. Dies kann direkt über eine Programmierschnittstelle erfolgen, oder durch ein sogenanntes Konfigurations-EPROM, in dem die Informationen fest gespeichert sind.

#### 2.4.1.1 Prinzipieller Aufbau der Cyclone II Serie

Zwischen den Ein-Ausgabe-Elementen an den Rändern des IC's verlaufen horizontal und vertikal durchgehende Bereiche mit Leitungen, über welche alle Verbindungen von und nach außen laufen. Zwischen den Bereichen mit den Leiterbahnen liegen sogenannte LABs (Logical Array Blocks) und EABs (Embedded Array Block). Die Logical Array Blocks setzen sich aus einzelnen logischen Elementen zusammen.

#### 2.4.1.1.1 Logic Array Block (LAB)

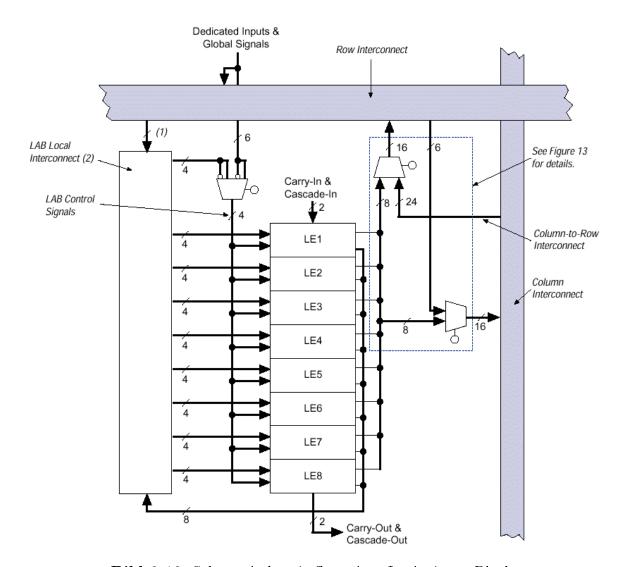

Ein Logic Array Block (LAB) besteht aus acht logischen Elementen, den zugehörigen Carry und Cascade Pfaden, den LAB-Steuersignalen und einem lokalen Verbindungsblock. Diese Grundstruktur des Bauelements ist in Bild 2.18 schematisch dargestellt. Die Eingangsdaten für die Elemente werden entweder aus den horizontalen Verbindungsbereichen oder von speziellen Eingangspins direkt geliefert. Die Ausgänge der Logischen Elemente werden sowohl zu den horizontalen wie auch den vertikalen Verbindungsbereichen und zu den Eingangsverknüpfungen des LAB geführt.

#### 2.4.1.1.2 Logikelement (LE)

Das Logikelement ist die kleinste logische Einheit eines ACEX 1K Bausteins. Jedes dieser Elemente enthält eine "Look Up Table (LUT)" mit vier Eingängen, je ein Element für Übertrags- und Kaskadiersignale (Carry Chain, Cascade Chain) und ein programmierbares Flipflop, das als D-, T-, JK- oder RS-Flipflop eingesetzt werden kann.

Bild 2.17: Blockschaltbild des Aufbaus der Cyclone II Serie.

Bild 2.18: Schematischer Aufbau eines Logic Array Block.

Bild 2.19: Schematischer Aufbau eines Logikelements.

Die LUT ist eine Art von Funktionsgenerator, der aus den vier Eingangsvariablen jede logische Verknüpfung erzeugen kann. Wird ein Logikelement ausschließlich für kombinatorische Logik eingesetzt, so wird der Ausgang des LUT am Flipflop vorbei, direkt zum Ausgang geführt. Die beiden Datenpfade Carry und Cascade sind Hochgeschwindigkeitsverbindungen zwischen den einzelnen Logikelementen. Der Carry Pfad unterstützt die Entwicklung von Zählern mit hohen Taktfrequenzen und der Cascade Pfad implementiert breitgefächerte Eingangsfunktionen mit einem Minimum an Laufzeitverlusten. Ein Logikelement kann in vier verschiedenen Betriebsarten eingesetzt werden:

- 1. "Normaler Betrieb",

- 2. "Arithmetische Betriebsart",

- 3. "Vorwärts/Rückwärts Zähler" und

- 4. "Rücksetzbarer Zähler".

#### "Normale Betriebsart"

Diese Betriebsart ist geeignet für allgemeine logische Anwendungen und für Dekodierschaltungen mit vielen Eingängen, die den Vorteil des Kaskadiersignals ausnützen. Hierbei werden die vier Dateneingänge und das Carry–In Signal als Eingangssignale für das logische Element benutzt.

#### **Normal Mode**

Bild 2.20: Schematischer Aufbau eines Logikelements in der Betriebsart 1.

#### **Arithmetic Mode**

Bild 2.21: Schematischer Aufbau eines Logikelements in der Betriebsart 2.

#### "Arithmetische Betriebsart"

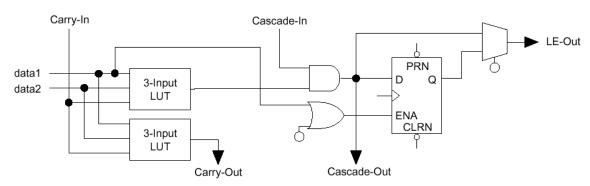

Dabei sind zwei LUT miteinander kombiniert. Aus dem ersten LUT, den zwei Eingangssignalen und dem Carry-In Signal wird das kombinatorische Ausgangssignal erzeugt. Diese Betriebsart eignet sich für Addierer, Akkumulatoren und Komparatoren, die die Vorteile des Carry-Out Signals ausnützen. Das Carry-Out Signal wird mit Hilfe des zweiten LUT und den drei gemeinsam genutzten Eingangssignalen erzeugt.

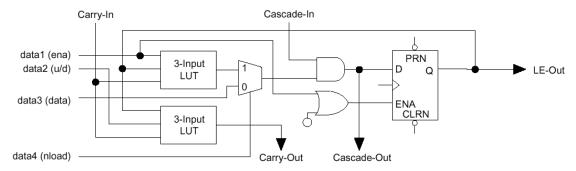

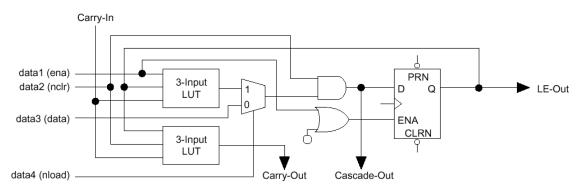

#### "Vorwärts/Rückwärts Zähler"

Diese Betriebsart nutzt zwei LUT's mit 3 Eingängen. Ein LUT erzeugt das Carry-Out Signal, das andere erzeugt das Zählsignal. Ein 2 zu 1 Multiplexer steuert das synchrone Laden eines Startwertes. Ein asynchrones Laden des Startwertes kann über die Signale Clear und Preset erfolgen. Zum Steuern des Vorwärts/Rückwärts Zählers stehen die Eingangssignale Counter Enable, Clock Enable, Up/Down, Data und nload zur Verfügung.

#### **Up/Down Counter Mode**

Bild 2.22: Schematischer Aufbau eines Logikelements in der Betriebsart 3.

#### **Clearable Counter Mode**

Bild 2.23: Schematischer Aufbau eines Logikelements in der Betriebsart 4.

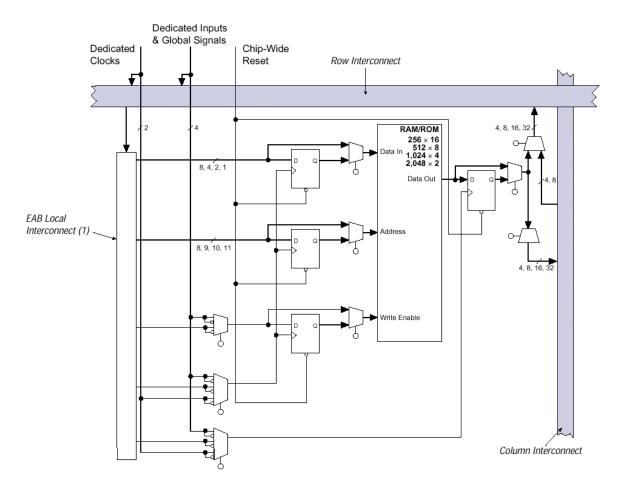

Bild 2.24: Konfiguration eines EAB als Single Port RAM.

#### 2.4.1.1.3 Embedded Array Block

EABs sind aus Blöcken flexibler RAM Zellen aufgebaut, jedes EAB kann aus 8 Eingängen und 16 Ausgängen jede logische Funktion realisieren. Durch verschalten mehrerer EABs können komplexe Schaltungen, wie Multiplizierer, Microcontroller und State Machines aufgebaut werden. Hauptsächlich werden EABs jedoch zur Speicherung von Daten genutzt, dazu besitzt jedes EAB 4096 Bit, aus denen Speicher unterschiedlicher Typen aufgebaut werden kann:

- RAM

- ROM

- Dual Port RAM

- FIFO

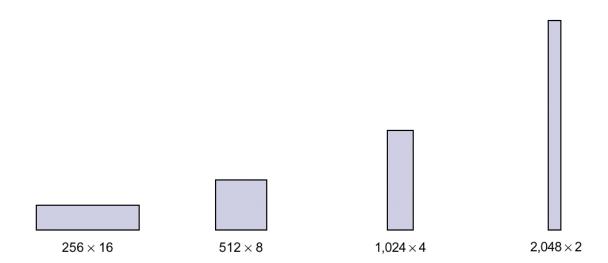

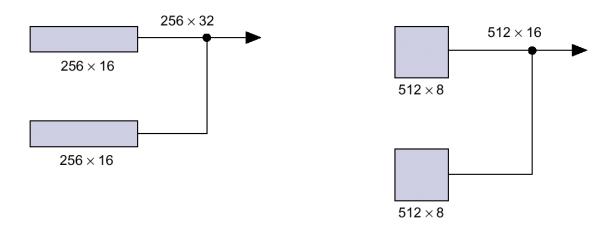

Wie erwähnt, stehen jedem EAB Block 4096 Bit zur Verfügung, diese Bits können unterschiedlich auf Speichertiefe und Speicherbreite verteilt werden. Mögliche Einteilungen der Speicherbreite sind aus Bild 2.25 zu entnehmen. Auch bei Nutzung der EABs als

Bild 2.25: Mögliche Speicherbelegung eines EAB.

Bild 2.26: Verschaltung zweier EABs.

Speicher besteht die Möglichkeit mehrere EABs miteinander zu verknüpfen. Durch diese Verknüpfung kann die Speicherkapazität erhöht werden. Es können jeweils nur EABs mit gleicher Speicherbreite verknüpft werden. Durch diesen Umstand ist lediglich die Speichertiefe, nicht aber die Speicherbreite, durch Kombination mehrerer EABs änderbar.

### 3 Eingabe von Schaltungsinformationen

#### 3.1 VHDL als Standardsprache

VHDL ist ein Ergebnis des "very high speed integrated circuit" (VHSIC) Programmes, das vom amerikanischen Verteidigungsministerium in den späten siebziger Jahren initiiert wurde, um die Grundlagen für eine neue Generation schneller hochintegrierter Schaltkreise zu schaffen. VHDL steht für VHSIC Hardware Description Language und ist seit 1986 IEEE Standard. Die heute aktuelle Version von VHDL hat die Bezeichnung IEEE–1164. VHDL kann eine recht schwer zu erlernende Sprache sein, wenn man nur das VHDL Language Reference Manual als Grundlage benutzt und versucht, sich alle Definitionen und Vereinbarungen anzueignen. Um eine Schaltung zu definieren benötigt man jedoch nur sehr selten den gesamten Vorrat an Möglichkeiten, so daß es meistens ausreicht, mit den wichtigsten Elementen dieser Sprache vertraut zu sein.

Für das Praktikum ist ein Erlernen der Sprache nicht notwendig, da hier nur exemplarisch eine kleinere Schaltung mit VHDL erstellt werden soll, um einen Vergleich mit den anderen Eingabemöglichkeiten zu haben. Aus diesen Grund ist der Einsatz von VHDL an dieser Stelle nur anhand einiger einfacher Beispiele aufgezeigt, was für die Bearbeitung des Versuches 1.3 ausreichend sein sollte. Als ausführliche Einführung ist das Buch VHDL von Douglas L. Perry, Mc Graw Hill Verlag zu empfehlen. Anhand von einfachen Beispielen sollen nun die grundlegenden Elemente der Sprache kurz erklärt werden. Alle Schlüsselwörter der Sprache VHDL sind in Großbuchstaben dargestellt. Zuerst soll als einfaches Beispiel ein D-Flipflop mit Enable-Eingang erläutert werden. Das D-Flipflop besitzt die folgenden Ein- und Ausgänge: Eine VHDL Beschreibung für

D - Signaleingang

CLK - Takteingang

CLRN - Clear Not Eingang

ENA - Enable Eingang

Q - Ausgang

dieses Flipflop könnte so aussehen:

```

LIBRARY ieee; -- Bibliotheksvereinbarung

USE ieee.std_logic_1164.all;

ENTITY dff IS -- Schaltungssymbol

PORT

(

d : IN STD_LOGIC;

```

```

clk

: IN STD_LOGIC;

clrn : IN STD_LOGIC;

: IN STD LOGIC;

: OUT STD_LOGIC

q

);

END dff;

ARCHITECTURE a OF dff IS -- Schaltungsbeschreibung

SIGNAL tmp : STD_LOGIC;

BEGIN

PROCESS (clk,clrn)

BEGIN

IF clrn = '0' THEN

tmp <= '0';

ELSIF (clk'EVENT AND clk = '1') THEN

IF ena = '1' THEN

tmp \le d;

ELSE

tmp <= tmp;

END IF;

END IF;

END PROCESS;

q \le tmp;

END a;

```

In den ersten beiden Zeilen sind die verwendeten Bibliotheken aus dem ALTERA-Entwicklungssystem beschrieben. Das Element IEEE.STD\_LOGIC\_1164.ALL aus der Bibliothek LIBRARY IEEE enthält alle Funktionen die für die Bearbeitung des Versuches 1.3 notwendig sind. In VHDL muß zuerst das Schaltungssymbol mit den Ein- und Ausgängen definiert werden. Dazu wird das Element ENTITY verwendet. Dieses Element ist die grundlegende Beschreibung eines Schaltungsentwurfs (building block). Die höchste Ebene des Entwurfs wird als top-level ENTITY bezeichnet. Wenn der Entwurf hierarchisch aufgebaut ist, wird die top-level Beschreibung lower-level Beschreibungen enthalten. Diese lower-level Beschreibungen werden dann auch als lower-level ENTITY bezeichnet.

Anschließend muß das Verhalten dieses Flipflops beschrieben werden. Die Schaltungsbeschreibung ist in der Zeile ARCHITECTURE A OF DFF IS definiert. Diese Schaltungsbeschreibung ist mit dem Namen "a" bezeichnet, da VHDL verschiedene Beschreibungen für ein Element zuläßt. Der Anfang dieser Beschreibung ist durch BEGIN und das Ende ist durch END A gekennzeichnet. Nach der ARCHITECTURE-Vereinbarung ist die lokale Variable TMP als Signal definiert, die identisch mit dem Ausgangssignal Q ist. Die Definition dieser Variablen ist notwendig, da während des Programmablaufes

auf Ausgangssignale nicht zugegriffen werden kann. Der Ausgangzustand des Flipflops wird daher in dieser lokalen Variable gespeichert und am Ende der ARCHITECTURE-Vereinbarung dem Ausgangssignal Q zugewiesen. Das ARCHITECTURE-Statement beinhaltet hier nur ein Statement, dass PROCESS-Statement. Dieses wiederum beinhaltet eine Reihe von Elementen:

- die sensitivity list,

- den process declarative part und

- den statement part.

In unserem Beispiel ist die sensitivity list der Teil, der nach dem Statement PRO-CESS in den Klammern steht, also clk und clrn. Der zweite Teil, der process declarative part ist der Bereich zwischen der sensitivity list und dem Wort BEGIN. Hier werden lokale Variable und Konstante definiert, die innerhalb des PROCESS-Statements benötigt werden, was in diesem Beispiel nicht der Fall ist. Der dritte Teil, der statement part, ist der gesamte Bereich zwischen BEGIN und END PROCESS. Alle Befehle in diesem Bereich werden wie bei allen Programmiersprachen sequentiell ausgeführt, d.h. die Reihenfolge der Befehle bestimmt die Reihenfolge der Ausführung. Innerhalb des statement parts stehen in diesem Beispiel nur IF (logische Bedingung) THEN-Anweisungen, die für dieses Beispiel vollkommen ausreichend sind. IF-STATEMENTS sollten immer so angeordnet werden, daß sich ein eindeutiger Entscheidungsbaum ergibt. Die Zuweisung eines logischen Pegels ('0' oder '1') bzw. des Wertes eines anderen Signales erfolgt über den Operator <=. Der Ausdruck CLK'EVENT AND CLK = '1' bezeichnet die ansteigende Flanke des clk-Signales. Neben dem IF-STATEMENT stehen natürlich noch viele andere Anweisungen zur Verfügung, von denen hier nur die CASE- und die LOOP-Anweisung erwähnt werden sollen. Ein CASE-STATEMENT erlaubt die Verzweigung bezüglich einer logischen Bedingung und kann für die behandelten Beispiele auch durch mehrere geschachtelte IF-STATEMENTS ersetzt werden.

```

CASE (expression) IS

WHEN constant_value1 =>

statement a;

statement b;

WHEN constant_value2 =>

statement c;

statement d;

WHEN OTHERS =>

statement e;

statement f;

```

Die LOOP-Anweisung ermöglicht es, Befehle innerhalb einer Schleife für verschiedene Werte einer Variablen nacheinander durchzuführen. Sie ist mit der for Anweisung der Programmiersprache PASCAL vergleichbar.

Bild 3.1: RS-Flipflop mit NAND-Gattern.

```

Label1:

FOR i IN 1 to 10 LOOP

statement1;

statement2;

END LOOP Label1;

```

VHDL erlaubt es auch, das zeitliche Verhalten einer Schaltung zu modellieren, z.B. durch Angabe der Gatterlaufzeiten. Eine solche Anweisung sieht für ein AND-Gatter mit den Eingängen A, B und dem Ausgang C folgendermaßen aus:

```

C <= A AND B AFTER 2ns;

```

Die Gatterlaufzeit wird hier durch das AFTER-STATEMENT auf 2 ns festgelegt. Diese Anweisung sollte allerdings innerhalb des ALTERA-Entwicklungssystems nicht angewendet werden, da die Gatterlaufzeiten durch den verwendeten Baustein bzw. der Umsetzung durch den Compiler vorgegeben werden. Neben dem im Beispiel oben definierten Standardsignalen (STD\_LOGIC) erlaubt VHDL eine Reihe weiterer Variablentypen, z.B. BIT, INTEGER, REAL etc. Es können auch Signale zu Vektoren zusammengefaßt werden. So wird z.B. mit

```

Q :OUT STD_LOGIC_VECTOR(1 TO 4)

```

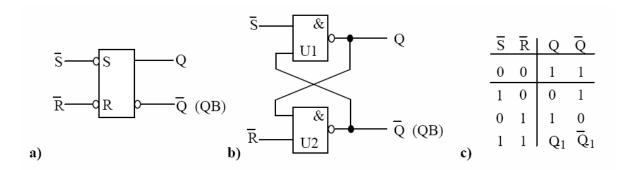

ein Ausgabevektor mit 4 Elementen definiert. Die Elemente können dann mit Q[1], Q[2] usw. ausgewählt werden. Als zweites Beispiel soll ein RS–Flipflop aus NAND–Gattern besprochen werden. Die logische Funktion der Schaltung läßt sich durch die Wahrheitstabelle (Bild 3.1.c) beschreiben. Um die Schaltung später beschreiben zu können, sind die beiden NAND–Gatter mit U1 und U2 gekennzeichnet. Eine mögliche Beschreibung dieses Flipflops könnte in VHDL so aussehen:

```

LIBRARY ieee; -- Bibliotheksvereinbarung

USE ieee.std_logic_1164.all;

ENTITY rsff IS -- Schaltungssymbol

PORT ( set , reset : IN STD_LOGIC;

```

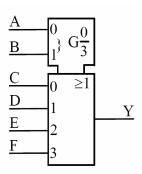

Bild 3.2: 4-zu-1 Multiplexer, logisches Schaltsymbol.

```

q , qb : OUT STD_LOGIC );

END rsff;

ARCHITECTURE a OF rsff IS -- Schaltungsbeschreibung

signal tmp1 : STD_LOGIC := '1';

signal tmp2 : STD_LOGIC := '0';

function und_nicht(a,b: STD_LOGIC) RETURN STD_LOGIC IS

variable c: STD_LOGIC;

BEGIN

c := NOT(A AND B);

RETURN c;

END und_nicht;

BEGIN

PROCESS (set, reset)

BEGIN

tmp1 <= und_nicht(tmp2,NOT(set));</pre>

tmp2 <= und_nicht(tmp1,NOT(reset));</pre>

END PROCESS;

q \le tmp1;

qb \le tmp2;

END a;

```

Beachten Sie, daß im Gegensatz zu Bild 3.1 die nicht negierten Eingangssignale set und reset verwendet werden. Hier wurden die NAND-Gatter als Unterfunktion und \_\_NICHT realisiert, um die Verwendung von Unterfunktionen zu erläutern. Die Deklaration FUNCTION und \_\_NICHT(A,B: STD\_LOGIC) RETURN STD\_LOGIC IS bedeutet, daß die Unterfunktion und \_\_NICHT mit den Variablen A und B vom Typ STD\_LOGIC aufgerufen wird und als Ergebnis eine Variable vom Typ STD\_LOGIC zurückliefert. Als letztes Beispiel soll ein 4-zu-1 Multiplexer beschrieben werden, dessen Schaltsymbol und Wahrheitstabelle in Bild 3.2 bzw. in Tabelle 3.1 angegeben sind. Die Beschreibung

| В | A | Y |

|---|---|---|

| 0 | 0 | С |

| 0 | 1 | D |

| 1 | 0 | Е |

| 1 | 1 | F |

Tabelle 3.1: 4-zu-1 Multiplexer, Wahrheitstabelle

dieses Bauelements in VHDL könnte folgendes Aussehen haben:

```

LIBRARY ieee; -- Bibliotheksvereinbarung

USE ieee.std_logic_1164.all;

Entity mux41 IS

PORT (c, d, e, f, a, b : IN STD_LOGIC;

y: OUT STD_LOGIC);

END mux41;

ARCHITECTURE a OF mux41 IS

BEGIN

PROCESS (c, d, e, f, a, b)

VARIABLE muxval : INTEGER RANGE 0 TO 3;

BEGIN

muxval := 0;

IF (a = '1') THEN

muxval := muxval + 1;

END IF;

IF ( b = '1' ) THEN

muxval := muxval + 2;

END IF;

CASE muxval IS

WHEN O =>

y <= c;

WHEN 1 =>

y \le d;

WHEN 2 =>

y <= e;

WHEN 3 =>

y \le f;

WHEN OTHERS =>

NULL;

END CASE;

END PROCESS;

END a;

```

### 3.2 AHDL (Altera Hardware Description Language)

Wie VHDL ist auch AHDL eine Sprache, und logische Schaltungen in Form eines "Programms" zu beschreiben. Von der Struktur her ist es vergleichbar mit der Programmiersprache C. Wie jede Eingabeform von Schaltungsinformation unterliegt auch die Beschreibung in AHDL bestimmten Regeln. Diese sind in aller Ausführlichkeit im MAX+PLUS® II AHDL-Handbuch nachzulesen. Wie bereits für VHDL gilt auch für AHDL, daß für das Praktikum ein Erlernen der Sprache nicht notwendig ist, da hier nur exemplarisch eine kleinere Schaltung mit AHDL erstellt werden soll, um einen Vergleich mit den anderen Eingabemöglichkeiten zu haben. Aus diesen Grund ist der Einsatz von AHDL an dieser Stelle nur anhand einiger einfacher Beispiele aufgezeigt.

Alle Schlüsselwörter der Sprache AHDL sind in Großbuchstaben dargestellt. Die reservierten Schlüsselwörter umfassen unter anderem alle logischen Funktionen, Flipflops und den logischen Anfangszustand X. Im MAX+PLUS® II-Programm sind eine Reihe von Eingabeschablonen für die Elemente von AHDL vorhanden. Unter Zuhilfenahme dieser "Templates" kann mit wenig Aufwand eine komplexe digitale Schaltung entworfen werden. Nachfolgend das Beispiel eines 4-zu-1 Multiplexers mit der Funktionsbeschreibung in einer CASE-Struktur.

```

SUBDESIGN mux_case

(

di[3..0]

: INPUT;

--Datenvektor

adr[1..0]

: INPUT;

--Adressvektor

: OUTPUT;

muxaus

)

BEGIN

CASE adr[] IS

WHEN O =>

muxaus=di[0];

WHEN 1 =>

muxaus=di[1];

WHEN 2 =>

muxaus=di[2];

WHEN 3 =>

muxaus=di[3];

END CASE;

END;

```

# 4 Kurzeinführung in Altera Quartus II

Die Entwicklungsumgebung Quartus II von Altera bietet alle Werkzeuge für den gesamten Ablauf eines komplexen Schaltungsentwurfs für programmierbare Logikbausteine. Von der Schaltungseingabe über die Synthese, die Simulation, die Programmierung bis zur Verifikation sind alle Elemente des Entwurfablaufs nahtlos im Programm integriert. Die Benutzerschnittstelle stellt sich als normale Windows-konforme Bedienoberfläche dar. Nach dem Starten des Programms öffnet sich das Hauptfenster mit den individuell anpassbaren Symbolleisten und Andockfenstern. Die Andockfenster können in der Symbolleiste ein- und ausgeschaltet werden. Die Bedeutung der einzelnen Schaltflächen wird beim Überfahren mit dem Mauszeiger eingeblendet. Neben den von anderen Programmen bekannten Menütiteln, wie File (Datei), Edit (Bearbeiten), View (Ansicht), Window (Fenster) und Help (Hilfe) gibt es die für Quartus spezifischen Menüs Project, Assignments und Processing. Die Bedeutung der Menüeinträge ist weitestgehend selbsterklärend. Neben der folgenden Kurzeinführung steht auch das Handbuch Introduction to Quartus II zur Verfügung.

## 4.1 Projektverwaltung

Prinzipiell sollte für jeden eigenen Teilentwurf, und sei er noch so klein, ein eigenes Projekt mit eindeutigem und selbsterklärendem Namen (z.B. fir\_filter) angelegt werden. Ein Projekt wird begonnen, indem es neu erstellt wird. Dies geschieht unter dem Menüeintrag File-New Project Wizard. In den sich dann öffnenden Dialogfenstern werden folgende Projekteinstellungen vorgenommen:

- 1. Angabe des Projektverzeichnisses (zur Vermeidung späterer Probleme sollte für jedes Projekt ein eigenes Verzeichnis angelegt werden), Angabe des Projektnamens und des Namens der obersten Hierarchiestufe des Entwurfs (diese sind normal identisch mit dem Verzeichnisnamen).

- 2. Angabe von Dateien, die dem Projekt hinzugefügt werden (für einfache Projekte keine).

- 3. Spezifizieren von externen Entwurfsprogrammen (trifft für das Praktikum nicht zu).

- 4. Angabe der Bausteinfamilie (hier: Cyclone II und Zuweisung eines spezifischen Bausteins auswählen).

- 5. Auswahl des Bausteins, im Praktikum wird der Typ EP2C70F672C6N verwendet.

- 6. Übersicht der Einstellungen.

Für Unterentwürfe ist ein Unterverzeichnis anzulegen, welches als User Library eingetragen wird (über Assignments-Settings-User Libraries). Dorthin kopiert man alle Dateien von eigenen Unterentwürfen. Werden sogenannte Megafunctions eingebunden, so sollten diese mit dem Projektnamen als Präfix und einem folgenden eindeutigen Bezeichner benannt (z.B. FIR\_FILTER\_MULTIPLIZIERER) und ebenfalls im Unterordner abgelegt werden. Der Namenspräfix ist wichtig, damit es in übergeordneten Projekten keine Teile mit identischem Namen gibt. Alle Unterentwürfe in einem Unterverzeichnis abzulegen hat Vorteile, wenn das Projekt in ein übergeordnetes Projekt eingebunden werden soll. In diesem Fall genügt es, die Dateien des Unterverzeichnisses und die Entwurfsdateien eines Projekts in das Unterverzeichnis des übergeordneten Projekts zu kopieren. Für jedes Projekt kann ein Symbol angelegt werden. Außer bei VHDL-Projekten, die eigene Packages verwenden, können die Symbole automatisch erstellt werden, ansonsten müssen sie manuell erstellt werden.

Beim Erstellen eines Projekts legt Quartus neben der Projektdatei mit der Dateiendung \*.qpf ("Quartus Project File") noch andere Dateien im Projektverzeichnis an, in denen die verschiedensten Einstellungen gespeichert sind. Ein bereits erstelltes Projekt kann unter dem Menüeintrag File-Open Project geöffnet werden. Nachdem ein Projekt erstellt oder geöffnet ist, sind links im Project Navigator die Hierarchie, die verwendeten Dateien (Files) und die Entwurfseinheiten (Design Units) aufgelistet. Der Project Navigator, wie auch andere Utility Fenster, können über die Utility Windows Symbolleiste oder über das Menü View-Utility Windows ein- und ausgeblendet werden. Es empfiehlt sich die Zoom Symbolleiste ebenfalls zur Symbolleistenfläche hinzuzufügen (über das Menü **Tools-Toolbars**). Das Projekt kann nun bearbeitet werden. Unter dem Menüeintrag File-Close Project wird das aktuelle Projekt geschlossen. Anderungen der Einstellungen werden implizit gespeichert. Ein kompletter Schaltungsentwurf beinhaltet verschiedene Dateien. Diese Dateien sind von der Bearbeitung her nebeneinander gleichberechtigt, werden jedoch durch den Zusammenhang im Entwurf hierarchisch strukturiert. Eine Datei, die zum Projekt gehören soll, kann unter dem Menüpunkt File-New oder über die Symbolleiste erstellt werden. Nach dem Auswählen des Menüpunktes erscheint ein Fenster, in dem die Art der zu erstellenden Datei ausgewählt werden kann. Zum Schaltungsentwurf stehen dabei die graphische Eingabe oder die Texteingabe zur Verfügung. Die für das Praktikum wesentlichen Dateitypen sind:

Unter dem Reiter "Device Design Files":

- Block Diagram/Schematic File mit der Dateiendung \*.bdf.

- VHDL File mit der Endung \*.vhd.

- AHDL File mit der Endung \*.tdf.

Unter dem Reiter "Other Files":

• Block Symbol File mit der Dateiendung \*.bsf.

• Vector Waveform File mit der Endung \*.vwf.

Nach dem Öffnen oder Neuerstellen einer Datei erscheint auch die zum Bearbeiten erforderliche Symbolleiste. Es können mehrere Dateien geöffnet und bearbeitet werden, die dann in einzelnen Unterfenstern im Arbeitsbereich von Quartus II erscheinen. Durch Aktivieren der einzelnen Unterfenster wird die spezifische Symbolleiste umgeschaltet. Die bearbeiteten Dateien können unter dem Menüpunkt **File-Save** oder über das Diskettensymbol auf der allgemeinen Symbolleiste gespeichert werden. Dabei wird bei mehreren geöffneten Dateien jeweils nur die aktuell aktive gespeichert. Beim Schließen des Projekts oder beim Beenden des Programms erfolgt eine automatische Abfrage für jede geöffnete und veränderte Datei, ob diese gesichert werden soll.

## 4.2 Grafische Eingabe (Block Diagram/Schematic)

Der grafische Editor dient zur Eingabe eines Schaltplans. In der zugehörigen Symbolleiste sind die Werkzeuge dargestellt, die zur Eingabe von Schaltungen eingesetzt werden können. Das Symbol Tool lässt sich auch durch Doppelklick in die freie Fläche des Editors aktivieren. Dabei öffnet sich ein Fenster, in dem selbst erstellte (unter dem Ordner Project) oder vordefinierte Symbole aus den mit Quartus II mitgelieferten Bibliotheken ausgewählt und in die zu erstellende Schaltung eingefügt werden können. Bei bekanntem Symbolnamen kann man diesen auch direkt im Auswahlfenster eingeben. Mit den verschiedenen Verbindungswerkzeugen (Node Tool, Bus Tool und Conduit Tool) lassen sich die eingefügten Elemente miteinander verbinden. Die wohl wichtigsten Elemente sind Ein- und Ausgänge, sie stehen unter den Namen input und output zur Verfügung.

## 4.2.1 Erstellen von Symbolen (Block Symbol)

Zur hierarchischen Strukturierung eines Entwurfs können Schaltungsteile zu eigenen Symbolen zusammengefasst werden. Dies kann man automatisiert vornehmen, indem der Menüpunkt File-Create/Update-Create Symbol Files for Current File gewählt wird. Bei komplexeren Schaltungen mit z.B. mehrdimensionalen Bussen ist das integrierte Werkzeug jedoch überfordert. Dann muss das Symbol von Hand erstellt werden. Dies geschieht durch öffnen einer Block Symbol Datei. Im grafischen Editor sieht man den Rahmenkonstrukt eines Symbols. Durch Anklicken der grünen Umrandung kann man Ein- und Ausgänge hinzufügen. Das Symbol muss unter identischem Namen, wie die Entwurfsdatei für die es stehen soll, abgespeichert werden (File-Save As)(mit der Endung \*.bsf, dem so genannten "Block Schematic File").

# 4.3 Erstellen von Textdateien (AHDL File oder VHDL File)

Neben der grafischen Eingabe von Schaltungen besteht die Möglichkeit des formalen Entwurfs mit den Beschreibungssprachen AHDL und VHDL. Hierzu wird eine Textdatei ebenso wie die vorigen Dateitypen erstellt und geöffnet. Beim Bearbeiten stehen unter

dem Menüpunkt **Edit-Insert Template** verschiedene Rahmengerüste für Anweisungskonstrukte unter AHDL und VHDL zur Verfügung.

## 4.4 Erstellen von Simulationsstimuli (Vector Waveform File)

Für die Simulation der erstellten Schaltungen muss ein Stimulus erstellt werden. Dazu wird eine so genannte Vector Waveform Datei erstellt oder geöffnet. Im linken Bereich kann durch Doppelklicken und Auswählen des Node Finder die im Entwurf erstellten und nach dem Compilieren vorhandenen Eingänge, Ausgänge und Knoten eingefügt werden. In der zugehörigen Symbolleiste stehen verschiedene Werkzeuge zum Erstellen von Takten, Pulsen und Zählungen zur Verfügung. Der Zeitumfang für die Simulation wird unter dem Menüpunkt **Edit–End Time** eingestellt. Die Datei muss vor der Simulation gespeichert werden. Der Dateiname ist dabei automatisch vorgegeben. Für hierarchische Schaltungsentwürfe mit mehreren Entwurfsdateien muss er allerdings mit dem Namen der zu simulierenden Einheit übereinstimmen.

## 4.4.1 Einrichtung der VWF-Editor ab Quartus II v11.1

- 1. Eine Verknüpfung der Datei " $C: \langle altera \rangle$ 11.1 $\langle quartus \rangle$ bin $\langle quartus \_sh$ " in Desktop Erstellen.

- 2. In die Zielfenster der Verknüpfung muss --qsim als Argument hinzugefügt werden.

- 3. Den Laufenden Projekt öffnen und eine Input Datei erstellen oder öffnen.

- 4. Nach dem die Stimulus fertig modifiziert wurde kann die Simulation direkt gestartet werden. Der Projekt muss nicht wieder Kompiliert werden, wenn er in Quartus II bereits kompiliert wurde.

# 4.5 Zuweisungen (Assignments)

Im Menü **Assignments** können verschiedenste Zuweisungen erfolgen. Dort gibt es Untermenüeinträge, über die die Ein- und Ausgänge des Entwurfs den Anschlüssen eines Bauteils zugeordnet (**Assignments–Assign Pins**) oder einzelne Schaltungsteile in bestimmte Bereiche eines Bausteins gelegt werden können.

# 4.6 Compiler und Simulator

Im **Processing** Menü sind alle Kommandos zusammengefasst, die für das Compilieren und die Simulation des Schaltungsentwurfs notwendig sind. In den meisten Fällen beschränkt sich das Prozedere auf den Start des Compilers und des Simulators über die allgemeine Symbolleiste. Nach dem Durchlauf öffnet sich automatisch ein Ergebnisfenster (Compilation Report oder Simulation Report) in dem die Ergebnisse betrachtet werden können.

## 4.6.1 Ergebnisfenster (Reports)

In den **Reports** werden die Ergebnisse der Compilierung oder der Simulation aufgelistet. Dabei werden nicht nur Fehlermeldungen ausgegeben, sondern auch eine Zusammenfassung, die Einstellungen, die vom Compiler generierten Gleichungen, die **Timing–Analysen** und mehr. Bei der Compilierung ist der Floorplan von besonderem Interesse. In ihm werden die realisierten Verbindungen und Belegungen des Bausteins angezeigt. Weiterhin kann man einzelne Verbindungen und die jeweils auf ihnen entstehenden Laufzeiten betrachten. Bei der Simulation wird im Report–Fenster das Ergebnis in einer der **Vector Waveform Datei** äquivalenten Form angezeigt. Aus den Report–Fenstern können die Ergebnisse dann auch ausgedruckt werden.

## 4.7 Programmierung

Das im Praktikum verwendete DSP-Kit wird mit einem so genannten Byte-Blaster Kabel per USB an den PC angeschlossen. Gestartet wird die Programmierung unter dem Menü **Tools-Programmer** oder über die allgemeine Symbolleiste. Im sich öffnenden Fenster wird links oben die verwendete Hardware eingestellt (Byte Blaster [USB0]). Falls die erforderliche Datei (Endung \*.sof "SRAM Object File") nicht angezeigt wird, muss sie hinzugefügt werden. Danach kann der Programmiervorgang gestartet werden.

# 5 Die Entwicklungsumgebung im Praktikum

In diesem Kapitel wird die Entwicklungsumgebung beschrieben, die Ihnen im Praktikum zur Verfügung steht. Zuerst wird auf die Hardware, also das Entwicklungsboard mit seinen Komponenten eingegangen.

## 5.1 Das Altera DSP Entwicklungs-Board

Das Development Board stellt dem Entwickler folgende Ein- bzw. Ausgabemöglichkeiten zur Verfügung:

- Analog I/O

- Zwei 14-bit analog-to-digital (A/D) Wandler mit 125 MSPS und 70 dB SNR

- Zwei 14-bit digital-to-analog (D/A) Wandler mit 165 MSPS und 70 dB SNR

- Ein 24-bit RGB VGA Adapter mit einem DB-15 Stecker

- Ein Audio CODEC mit Eingang, Ausgang, und verstärktem Ausgang

- Memory Subsystem

- 256 Mbyte DDR2 SDRAM DIMM

- 1 Mbyte synchronous SRAM (SSRAM)

- Zwei EPCS64 64 Mbit seriell Konfigurationsbausteine

- Debugging Interface-Mictor Stecker zum Hardware und Software debugging

- Erweiterungsschnittstellen

- 3.3-V/5-V tolerant Altera expansion/prototype headers

- Ein Texas Instruments Evaluation Module (TI-EVM) Erweiterungsstecker

- Zwei sieben-segment LED Anzeigen

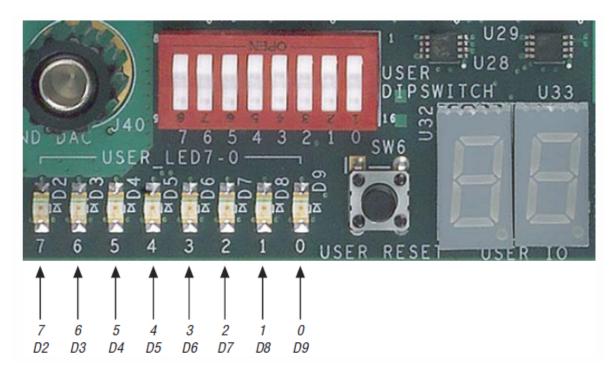

- Acht benutzerdefinierte LEDs

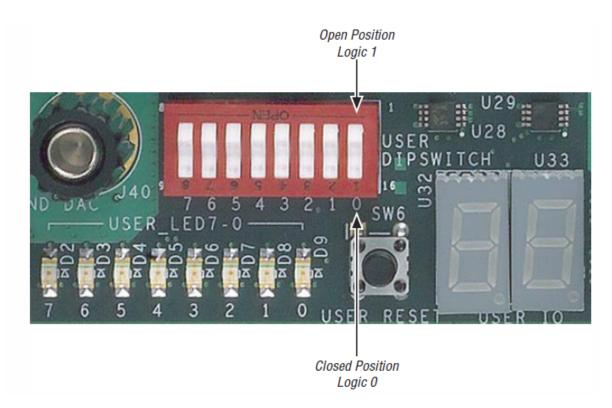

- Ein benutzerprogrammierbarer DIP Schalter (8 Positionen)

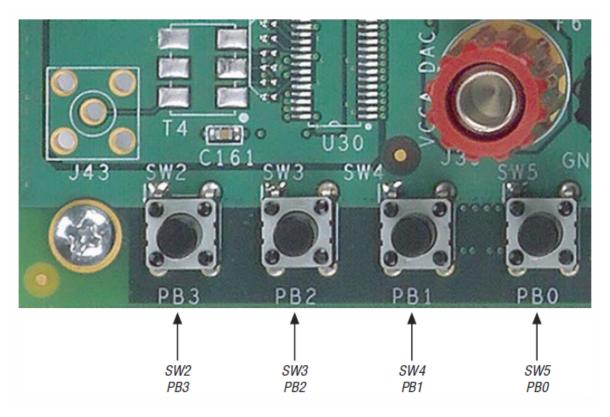

- Vier benutzerprogrammierbare Taster

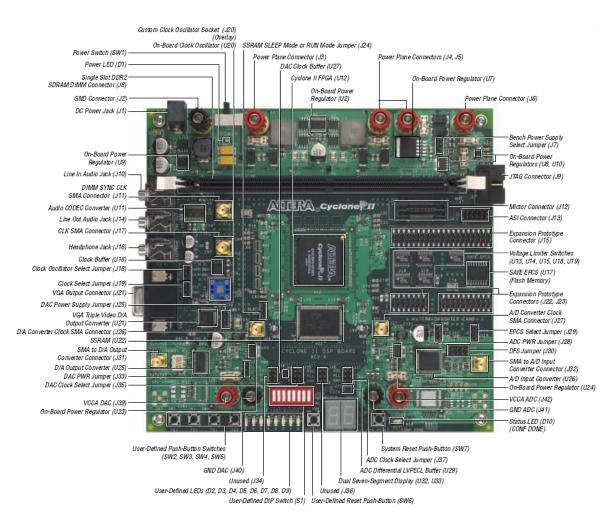

Das zentrale Element bildet der programmierbare Logikbaustein EP2C70F672 von Altera. Eine Übersicht des gesamten Boards zeigt Bild 5.1. Die für das Praktikum wichtigsten Komponenten sollen im Folgenden kurz vorgestellt werden.

Bild 5.1: Übersichtsdarstellung des Altera Boards.

#### 5.1.1 Der Altera EP2C70F672 Baustein

Aufgrund seiner Komplexität wird der Baustein den Field Programmable Gate Array Devices (FPGA) zugeordnet. Er besitzt ein 672-pin FineLine-BGA-Gehäuse (FBGA), wobei fast jeder zweite Pin entweder für Masse oder eine der beiden Versorgungsspannungen reserviert ist. Es stehen noch 422 benutzerdefinierte I/O-Ports zur Verfügung. Die Spannungen sind zum Einen die interne Versorgungsspannung von 1,8 V und zum Anderen die Spannung der I/O-Pins, die 3,3 V beträgt. Die logischen Eigenschaften des Bausteins sind in Tabelle 5.1 aufgelistet. Auf die einzelnen Elemente wird in den folgenden Unterkapiteln näher eingegangen.

| Embedded $18 \times 18$ multipliers        | 150     |

|--------------------------------------------|---------|

| Logic Elements (LEs)                       | 68416   |

| M4K RAM blocks (4 Kbits + 512 parity bits) | 250     |

| Maximum differential channels              | 262     |

| PLLs                                       | 4 PLLs  |

| Total RAM Bits                             | 1152000 |

| User I/O Pins                              | 422     |

Tabelle 5.1: Eigenschaften des CPLD Bausteins.

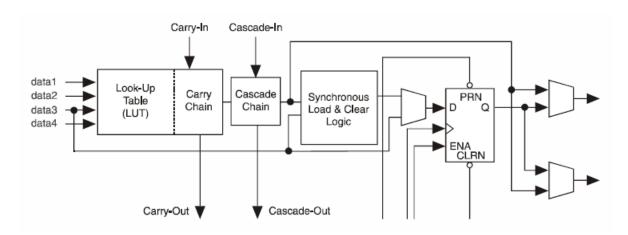

## 5.1.1.1 Das Logic Element (LE)

Die kleinste Einheit des Bausteins bildet das Logic Element. Es besteht aus einer 4-Bit Look Up Table (LUT), in welcher die logischen Verknüpfungen abgelegt werden. Desweiteren ist ein programmierbares Register vorhanden, welches wahlweise als D-, T-, JK- oder RS-Flipflop eingesetzt werden kann. Als Ausgang steht das Ergebnis der LUT direkt und/oder im Ausgangsregister zwischengespeichert zur Verfügung. Bild 5.2 zeigt den vereinfachten Aufbau eines LEs. Für schnelle arithmetische Operationen gibt es eine spezielle Carry-Chain und für breite Funktionen eine Cascade-Chain, die die einzelnen LEs verbindet. Das LE kann in drei verschiedenen Modi programmiert werden. Dies sind der Counter Mode, der Arithmetic Mode und der Normal Mode, welche jeweils spezielle Vorteile bei bestimmten Schaltungen besitzen. Der Compiler übernimmt die Modi-Einstellung vollautomatisch, wenn nicht vom Benutzer eine bestimmte Vorgabe besteht.

## 5.1.1.2 Der Logic Array Block (LAB)

Jeweils zehn LEs bilden einen Logic Array Block. Innerhalb dieses Blockes gibt es schnelle lokale Verbindungen. Ein LAB besitzt je zwei clock und clock enable Signale. Alle LEs innerhalb des LABs können nur auf diese Signale zurückgreifen. Die clock enable-Signale gelten für den gesamten Block. Wird insbesondere von einem Taktsignal sowohl die steigende als auch die negative Flanke benötigt, so werden hierfür schon beide

Bild 5.2: Vereinfachter Aufbau eines Logic Elements.

Bild 5.3: Die MegaLAB-Struktur.

clock-Leitungen des LABs belegt. Benötigt ein LE einen anderen Takt, so muss es in einem anderen LAB platziert werden.

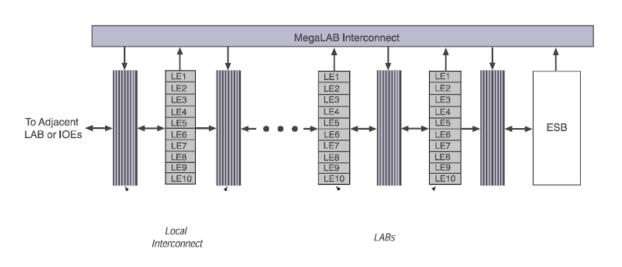

#### 5.1.1.3 Die MegaLAB-Struktur

In einer MegaLAB-Struktur sind 16 LABs und ein ESB gruppiert. Bild 5.3 veranschaulicht diese Hierarchie. Die lokalen Verbindungen und die sogenannten MegaLAB Verbindungen sind in diesem Schaubild ebenfalls dargestellt.

## 5.1.1.4 Der Embedded System Block (ESB)

Eine Besonderheit der Cyclone II Architektur stellt der Embedded System Block dar. Mit ihm kann entweder ein Set von Makrozellen oder Speicher realisiert werden. Dieser variable Einsatzbereich erhöht die Flexibilität des gesamten Bausteins. Hinsichtlich der

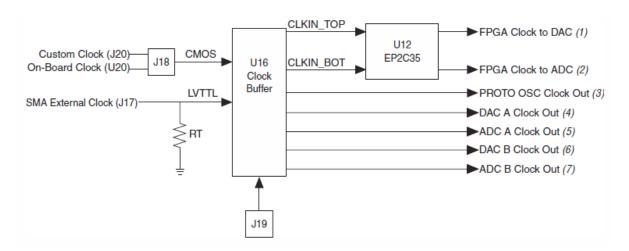

Bild 5.4: Taktverteilung des Altera Entwicklungs-Boards.

Clock- und Steuersignale gelten dieselben Einschränkungen wie bei den LEs innerhalb eines LABs (siehe Kap. 5.1.1.2). Wird der ESB als Speicher konfiguriert, so stehen eine Vielzahl von Organisationstypen (ROM, dual-port RAM, FIFO, CAM) zur Auswahl. Auch die Adressierung der 2048 Bits pro ESB ist variabel und reicht von 2048 × 1 bis 128 × 16. Breitere oder tiefere Speicher werden durch Kombination mehrerer Blöcke ermöglicht. Die Betriebsart dual-port RAM erlaubt gleichzeitiges schreiben und lesen des Speichers von verschiedenen Adressen. Der Programmierer muss allerdings sicherstellen, dass nicht simultan auf dieselbe Adresse zugegriffen wird, sonst ist das Ergebnis nicht vorhersagbar.

### 5.1.1.5 Globale Signale

Es gibt acht besonders ausgelegte globale Verbindungen auf dem Chip, wobei vier davon für Taktsignale reserviert sind (siehe Kap. 5.1.2). Die übrigen vier stehen dem Entwickler zur freien Verfügung. Sie können entweder von einem externen Signal oder von interner Logik betrieben werden. Findet der Quartus-Compiler ein asynchrones Reset- oder Setsignal, so legt er dieses automatisch auf eine der globalen Leitungen, falls eine davon verfügbar ist.

#### 5.1.2 Taktung und PLLs

Die Taktverteilung des Altera Entwicklungs-Boards ist in Bild 5.4 dargestellt. Zunächst muss der Takt definiert werden. Dies geschieht mit Hilfe des clock-buffers U16. Dieser generiert acht identische clock-Ausgänge (davon ist ein Ausgang nicht verbunden und zwei Ausgänge nicht in Verwendung), die auf dem Board zur Verfügung stehen. Der Takt kann dabei aus den folgenden Optionen gewählt werden:

- Verwendung des on-board Taktoszillator mit 100 MHz (U20)

- Verwendung eines eigenen Taktoszillators (Ersatz des 100 MHz Oszillators in U20)

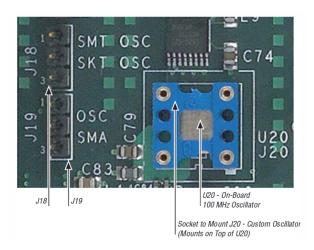

Bild 5.5: U20/J20, J18 & J19 für die Einstellung des Taktes.

• Verwendung eines externen Taktes über die SMA Stecker (J20)

In Bild 5.5 ist der on-board Oszillator und die Jumper zur Einstellung dargestellt. Für die Versuche im Rahmen dieses Praktikums ist der on-board Oszillator völlig ausreichend. Für einige Versuchsteile muss er sogar zusätzlich intern verringert (geteilt) werden, um z.B. die Verschiebung im Lauflichtversuch für das menschliche Auge sichtbar zu machen. Die Zuweisung des Global Clock innerhalb der Praktikumsversuche geschieht über die Pinnumer N25.

Cyclone® II Bausteine besitzen bis zu vier phase-locked Schleifen (PLLs), die robustes Taktgebermanagement bzw. -synthese für Vorrichtungstaktgebermanagement, Taktgebermanagement des externen Systems und Input-/Outputschnittstellen zur Verfügung stellen. Cyclone II PLLs sind vielseitig einsetzbar und können als Nullverzögerungspuffer, Jitterdämpfer oder Frequenzsynthesizer verwendet werden. Die bis zu vier PLLs unterstützen fortgeschrittene Funktionen, wie Taktgeberumschalten und programmierbares Umschalten. Diese PLLs bieten die Möglichkeit der Taktgebervervielfachung bzw. -reduzierung, Phasenverschiebung und programmierbarer Taktzyklen und können verwendet werden, um Taktgeberverzögerungen herabzusetzen bzw. zu justieren. Die Cyclone II Familie unterstützt zudem auch einen Energiesparmodi, in dem unbenutzte Taktgebernetze abgestellt werden können. Die Altera Quartus II Software bietet Zugriff auf die PLLs und ihren Eigenschaften ohne irgendwelche externen Vorrichtungen zu erfordern. Die bis zu vier PLLs sind in den vier Ecken des Bausteins angeordnet. Der Hauptzweck einer PLL ist es, die Phase und die Frequenz des VCO zu einem Bezugstaktgeber zu synchronisieren. Es gibt einige Bestandteile, die eine PLL enthalten, um diese Phasenausrichtung zu erzielen. Ausführliche Details zur Verwendung der PLLs der Cyclone II Familie findet sich unter http://www.altera.com/literature/hb/cyc2/ cyc2\_cii51007.pdf.

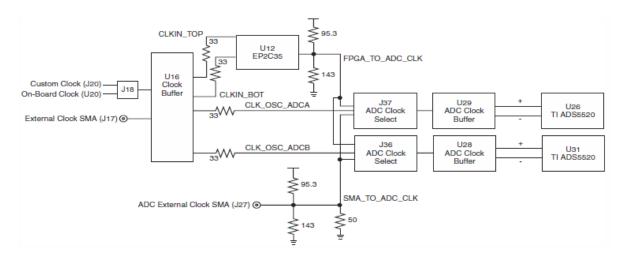

Bild 5.6: Schematische Darstellung der Taktoptionen der A/D-Wandler.

## 5.1.3 A/D-Wandler

Es sind zwei 14 Bit A/D–Wandler vom Typ TI ADS5500 auf dem Entwicklungs–Board vorhanden. Das Signal–to–noise–ratio (kurz: SNR) beträgt 70 dB für Eingangssignale von 1 MHz bis zur Nyquistfrequenz der Wandler. Die maximale Eingangsspannung der Wandlereingänge beträgt  $2, 2V_{PP}$ . Das Datenformat des gewandelten Analogsignals kann durch Jumper (J30 für Kanal A und J38 für Kanal B) auf dem Board eingestellt werden. Tabelle 5.2 gibt die möglichen Datenformate wieder (für den Versuch mit digitalen Filtern kann hier das standardmäßig eingestellte Zweierkomplement–Datenformat verwendet werden!). Bild 5.6 zeigt die Komponenten, die für die Taktauswahl für den A/D–Wandler TI ADS5500 (U26 für Kanal A, U31 für Kanal B) verwendet werden. Die Jumper J37 (Kanal A) oder J36 (Kanal B) wählen das Taktsignal aus folgenden Möglichkeiten:

- on-board Oszillator,

- FPGA Takt oder

- externer SMA-Takt.

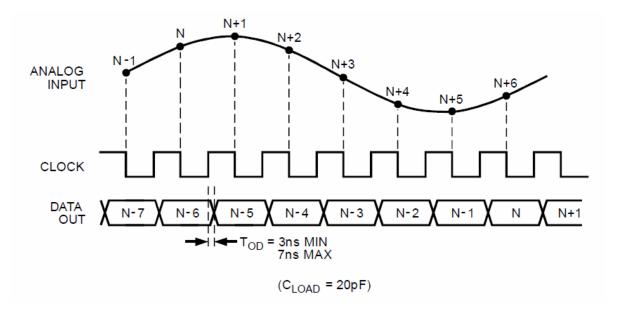

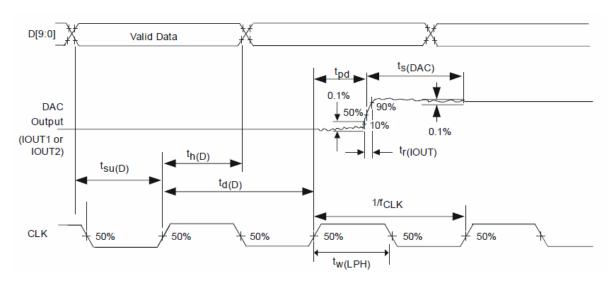

Das gewählte Taktsignal wird über einen differentiellen LVPECL Buffer (U29 für Kanal A, U28 für Kanal B) an den Wandlereingang geführt. Eine schematische Darstellung eines Wandelvorganges ist in Bild 5.7 in Form des Timingdiagramms dargestellt. Zur Verwendung der A/D-Wandler in den Versuchen sind die Pinzuweisungen nach Tabelle 5.3 für Kanal A und Tabelle 5.4 für Kanal B notwendig. Beachten Sie dabei die zusätzlichen Pinnummern, die manuell auf GND und  $V_{CC}$  zu legen sind!

### 5.1.4 D/A-Wandler

Auf dem Entwicklungs-Board sind zwei 14 Bit D/A-Wandler vom Typ TI DAC904E

Bild 5.7: Timingdiagramm A/D-Wandler.

| Jumper (J30 & J38) | Data             | Clock output                       |

|--------------------|------------------|------------------------------------|

| Einstellung        | Format           | Polarität                          |

| Pins 1 und 2       | Zweierkomplement | Daten gültig bei fallender Flanke  |

| Pins 3 und 4       | Binär            | Daten gültig bei fallender Flanke  |

| Pins 5 und 6       | Zweierkomplement | Daten gültig bei steigender Flanke |

| Pins 7 und 8       | Binär            | Daten gültig bei steigender Flanke |

${\bf Tabelle~5.2:~Einstellbare~Datenformate~der~A/D-Wandler.}$

| A/D-Wandler | A/D-Wandler | Cyclone II                             | A/D-Wandler | A/D-Wandler | Cyclone II            |

|-------------|-------------|----------------------------------------|-------------|-------------|-----------------------|

| Pinname     | Pinnummer   | Pinnummer                              | Pinname     | Pinnummer   | Pinnummer             |

| ADC_A_CLK_N | 11          |                                        | ADC_A_D5    | 52          | C11                   |

| ADC_A_CLK_P | 10          |                                        | ADC_A_D6    | 53          | B12                   |

| ADC_A_CM    | 17          |                                        | ADC_A_D7    | 54          | D13                   |

| ADC_A_DCLK  | 43          | A13                                    | ADC_A_D8    | 55          | B22                   |

| ADC_A_DFS   | 40          |                                        | ADC_A_D9    | 56          | A21                   |

| ADC_A_INM   | 20          |                                        | ADC_A_D10   | 60          | A23                   |

| ADC_A_INP   | 19          |                                        | ADC_A_D11   | 61          | B23                   |

| ADC_A_IREF  | 31          |                                        | ADC_A_D12   | 62          | C22                   |

| ADC_A_OE    | 41          | $\mathrm{F7} \rightarrow \mathrm{VCC}$ | ADC_A_D13   | 63          | A22 (MSB)             |

| ADC_A_OVR   | 64          | D15                                    | ADC_A_REFM  | 30          |                       |

| ADC_A_D0    | 44          | C5 (LSB)                               | ADC_A_REFP  | 29          |                       |

| ADC_A_D1    | 45          | C6                                     | ADC_A_SEN   | 4           | B18                   |

| ADC_A_D2    | 46          | В7                                     | ADC_RESET   | 35          | $T24 \rightarrow GND$ |

| ADC_A_D3    | 47          | A8                                     | ADC_SCLK    | 2           | AD24                  |

| ADC_A_D4    | 51          | A9                                     | ADC_SDATA   | 3           | Y1                    |

${\bf Tabelle~5.3:~A/D~ADS5500~A/D-Wandler~Pinnummern~f\"ur~Kanal~A}.$

| A/D-Wandler | A/D-Wandler | Cyclone II           | A/D-Wandler | $\mathbf{A}/\mathbf{D}$ -Wandler | Cyclone II            |

|-------------|-------------|----------------------|-------------|----------------------------------|-----------------------|

| Pinname     | Pinnummer   | Pinnummer            | Pinname     | Pinnummer                        | Pinnummer             |

| ADC_B_CLK_N | 11          |                      | ADC_B_D5    | 52                               | B20                   |

| ADC_B_CLK_P | 10          |                      | ADC_B_D6    | 53                               | A20                   |

| ADC_B_CM    | 17          |                      | ADC_B_D7    | 54                               | B21                   |

| ADC_B_DCLK  | 43          | C13                  | ADC_B_D8    | 55                               | F18                   |

| ADC_B_DFS   | 40          |                      | ADC_B_D9    | 56                               | G18                   |

| ADC_B_INM   | 20          |                      | ADC_B_D10   | 60                               | E18                   |

| ADC_B_INP   | 19          |                      | ADC_B_D11   | 61                               | F20                   |

| ADC_B_IREF  | 31          |                      | ADC_B_D12   | 62                               | D21                   |

| ADC_B_OE    | 41          | $R2 \rightarrow VCC$ | ADC_B_D13   | 63                               | D20 (MSB)             |

| ADC_B_OVR   | 64          | A6                   | ADC_B_REFM  | 30                               |                       |

| ADC_B_D0    | 44          | F17 (LSB)            | ADC_B_REFP  | 29                               |                       |

| ADC_B_D1    | 45          | D17                  | ADC_B_SEN   | 4                                | D19                   |

| ADC_B_D2    | 46          | D18                  | ADC_RESET   | 35                               | $T24 \rightarrow GND$ |

| ADC_B_D3    | 47          | C19                  | ADC_SCLK    | 2                                | AD24                  |

| ADC_B_D4    | 51          | B19                  | ADC_SDATA   | 3                                | Y1                    |

Tabelle 5.4: A/D ADS5500 A/D–Wandler Pinnummern für Kanal B.

integriert. Den zeitlichen Ablauf einer Wandlung zeigt exemplarisch Bild 5.8. In Tabelle 5.5 und Tabelle 5.6 sind die dazugehörigen Parameter angegeben. Der D/A–Wandler arbeitet mit der positiven Taktflanke und das analoge Ausgangssignal liegt um einen Takt und  $t_{pd}$  verzögert am Ausgang an. Zu beachten ist hierbei, dass sich die Verzögerung auf einen Takt des D/A–Wandlerbausteins bezieht, der unabhängig vom A/D–Wandlertakt sein kann. Die Signalverzögerung summiert sich somit zu einem D/A–Wandlertakt plus 1 ns. In den in dieser Arbeit behandelten Projekten kann diese Verzögerung allerdings vernachlässigt werden, da sich eine Messung der Verzögerungszeiten der Filter nur bei einem externen Takt von maximal 500 kHz anbietet.

Bild 5.8: Exemplarischer Timingdiagramm einer D/A-Wandlung.

Der D/A-Wandler wird bei den Praktikumsprojekten immer mit 100 MHz betrieben (siehe Kap. 5.1.2), somit fällt seine Verzögerungszeit gegenüber einer Abtastperiodendauer nicht ins Gewicht. Die D/A-Wandler werden über die SMA-Stecker mit dem Interface des TI DAC904E Wandlerbausteins mit Kabeln verbunden. Die D/A-Wandlerbausteine liefern ein 14 Bit aufgelöstes Signal mit einer Datenrate bis zu 165 MSPS. Das Signal-to-noise-ratio (kurz: SNR) beträgt 70 dB für Ausgangssignale von 1 MHz bis zur Nyquistfrequenz der Wandler. Die beiden Wandler sind den logischen Kanälen A und B zugeordnet. Zur Verwendung müssen die in Tabelle 5.7 bzw. Tabelle 5.8 angegebenen Pinzuweisung durchgeführt werden. Das Datenformat der D/A-Wandlerbausteine ist Einerkomplement!

#### 5.1.5 Speicherbausteine

Auf dem Board befinden sich noch zwei RAM-Bausteine von IDT mit je 64 K  $\times$  16 Bit. Sie besitzen eine Zugriffs- und Zykluszeit von 12 ns. Die korrekte Ansteuerung muss der Programmierer sicherstellen. Im Rahmen dieses Praktikums wird der externe Speicher nicht direkt verwendet.

| Parameter                                   | Test Conditions                              | Min. | Typ. | Max. | Unit            |

|---------------------------------------------|----------------------------------------------|------|------|------|-----------------|

| Analog output                               |                                              |      |      |      |                 |

| f                                           | $DV_{DD} = 4,5 \text{ V to } 5,5 \text{ V}$  | 100  | 125  |      | Mada            |

| $f_{CLK}$ Maximum output update rate        | $DV_{DD}=4,5~\mathrm{V}$ to $5,5~\mathrm{V}$ | 70   | 100  |      | MSPS            |

| $t_{sDAC}$ Output settling time to $0,1~\%$ |                                              |      | 35   |      | ns              |

| $t_{pd}$ Output propagation delay           |                                              |      | 1    |      | ns              |

| GE Glitch energy                            | Worst case LSB transition (code 511 – 512)   |      | 5    |      | pV-s            |

| $t_{r(IOUT)}$ Output rise time 10 to 90 %   |                                              |      | 1    |      | ns              |

| $t_{f(IOUT}$ Output fall time 90 to 10 $\%$ |                                              |      | 1    |      | ns              |

| Output poice                                | $IOUT_{FS} = 20 \text{ mA}$                  |      | 15   |      | $\frac{pA}{Hz}$ |

| Output noise                                | $IOUT_{FS} = 2 \text{ mA}$                   |      | 10   |      | $\overline{Hz}$ |

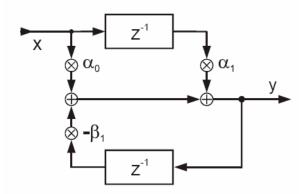

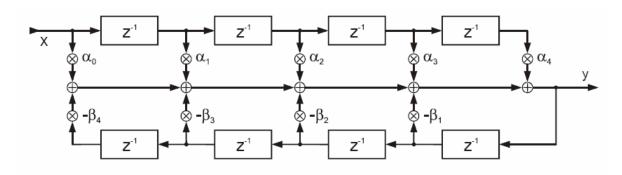

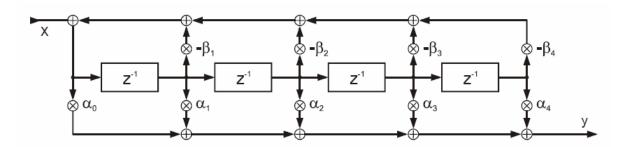

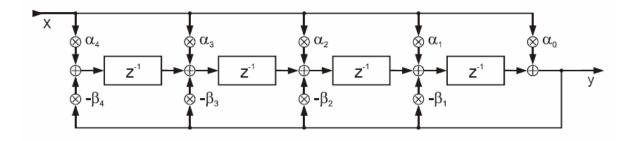

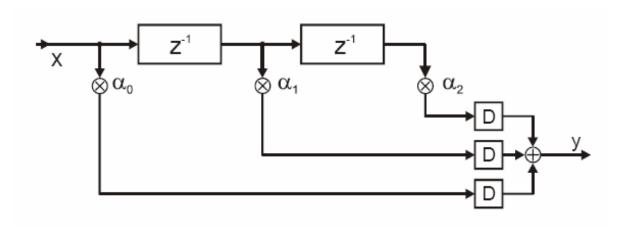

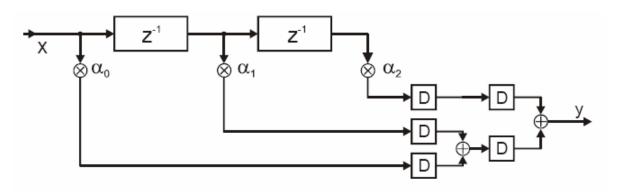

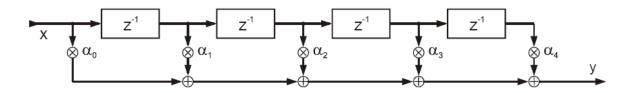

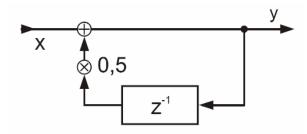

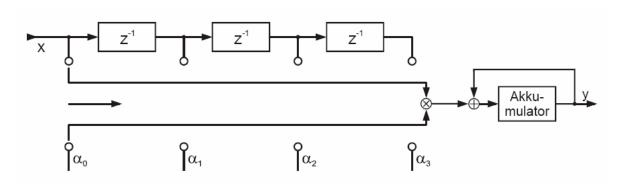

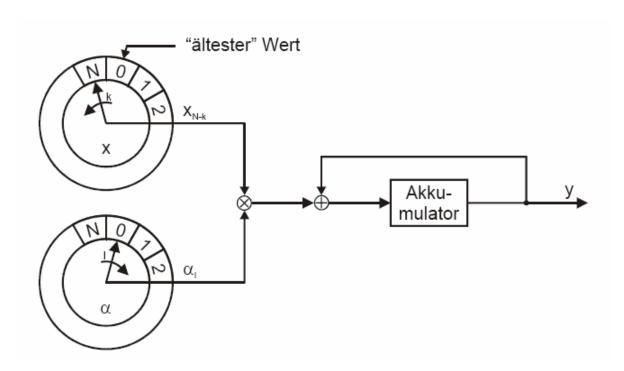

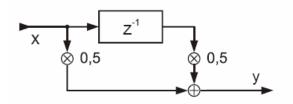

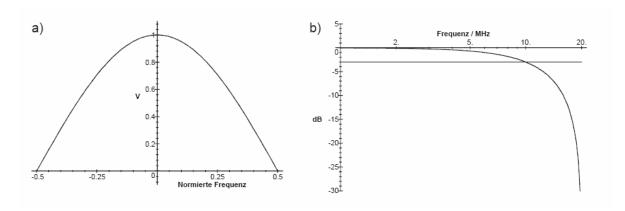

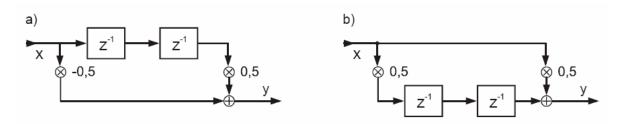

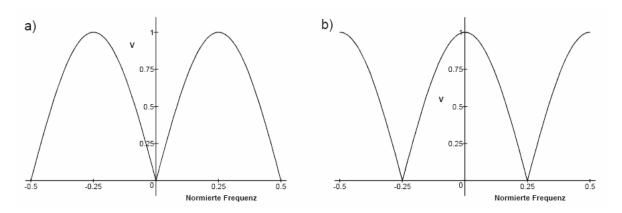

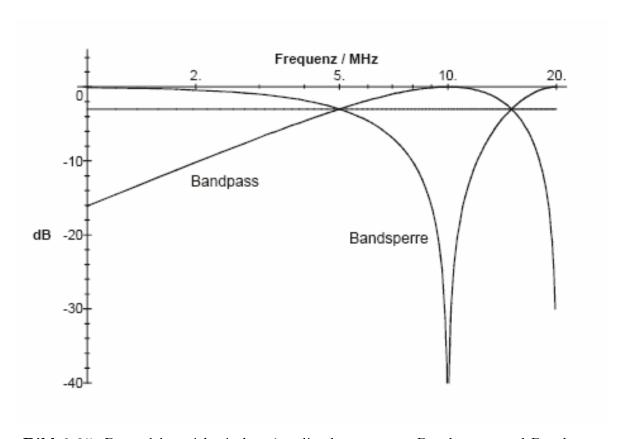

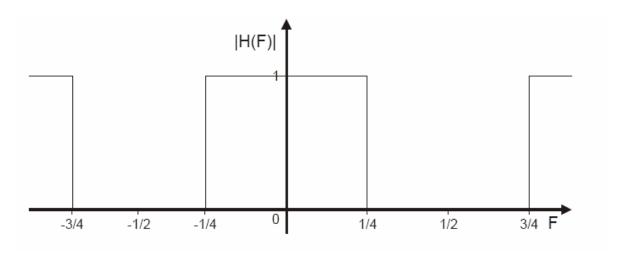

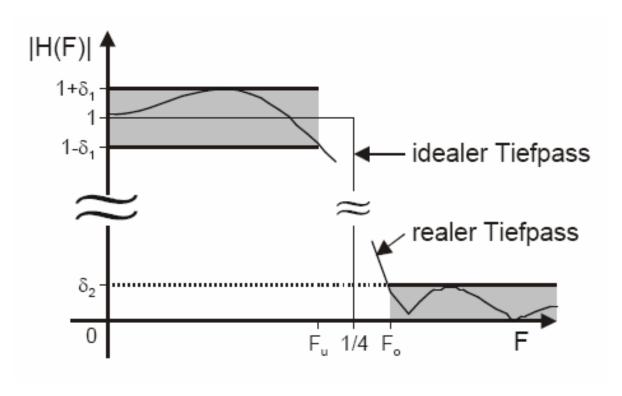

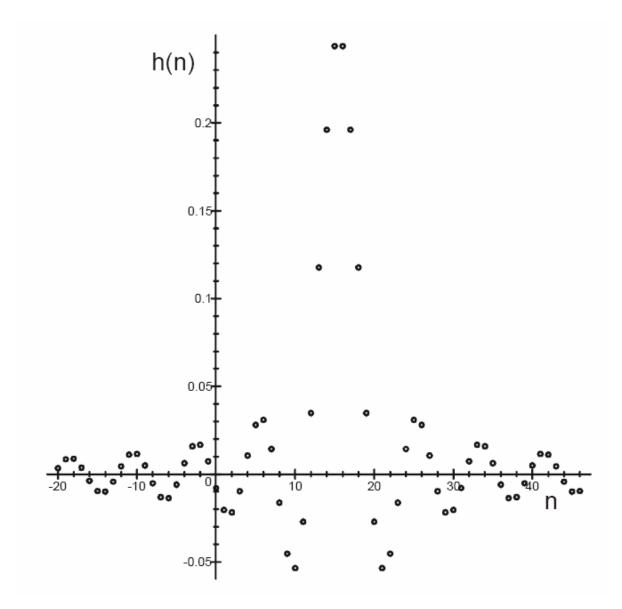

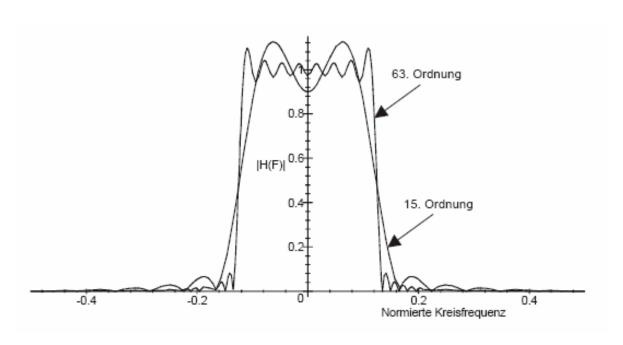

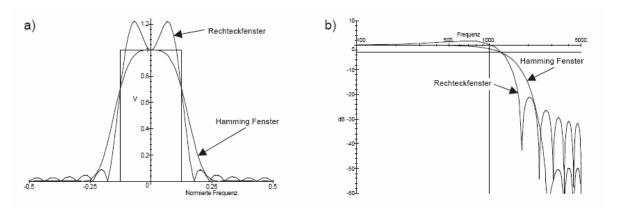

${\bf Tabelle~5.5:~AC~Spezifikationen~des~D/A-Wandlers.}$